前言 :

隨著IC製程逐步降低, IC 功耗跟著減少, 在10奈米製程以下的 Core-chip,其工作電壓早隨之下降至 1.2V 以下, 但由於周邊電子器件非主要核心, 其產品電壓也都在 3.3V, 5V 之林,因此應用上使用到電平轉換 IC 的機會也逐漸增加, 伴隨而來的一些應用問題也是層出不窮,說到電平轉換 IC, 其主要選用需考量 :

- IO 種類, 市場上大多為 Open-drain 設計以及 Push-pull 設計.

- 電壓, 須看 IC 兩端的電壓是否符合 IC 規格.

- 應用頻寬, 當指該電平轉換 IC 最大支持速度, 但不建議用到剛好, 而是應該像示波器用法一樣, 最大頻寬應為最大速度的 1/2 ~ 1/3.假設該 IC 最大速度為 50MHz, 則其最大頻寬建議 33MHz 以下.

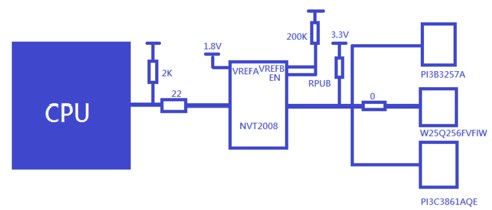

本章節講到的案例, 為 NXP 8 Bit 電平轉換 IC NVT2008PW 的應用案例,其應用方塊圖如下 :

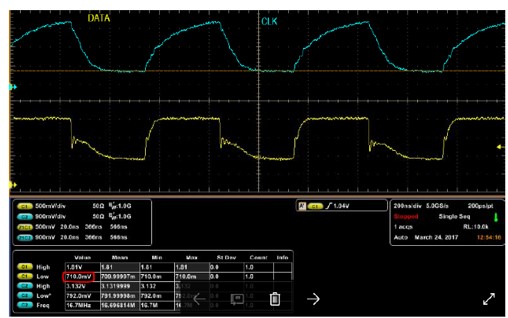

可看到 NVT2008 低壓端為 1.8V 至 CPU, 而 3.3V 端有並聯 3 個 SPI Device.而在 SPI Flash W25Q256FVFIW端看到失敗的波形 :

我們看到藍色的上升波形完全 Fail, 而且對地的 Offset 達到 710mV, 已經接近 3.3V * 0.3 = 0.99V 的限制.

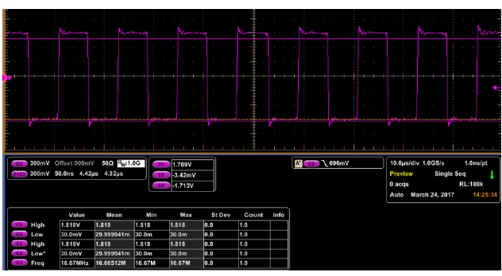

但是在 1.8V 端的波形則是很完整的方波對地

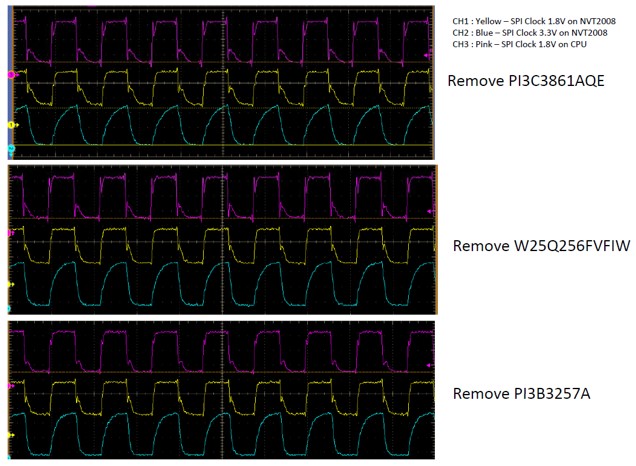

陸續移除後面的 3 個 Devices, 肉眼可見到波形的上升有逐步改善

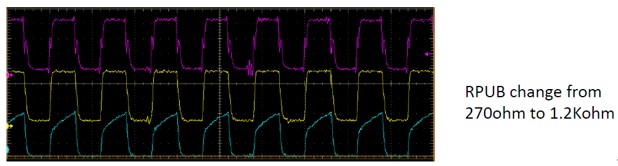

3.3V 端有 Pull high 電阻, 將其由 270.歐姆改為 1.2K歐姆則看到對地 Offset 有明顯下降

而對地 Offset 問題發現在 CPU 端有串聯 22歐姆的電阻, 將其改為 0 歐姆便馬上將 Offset 下壓到 510mV.

結論 :

由以上波形的實驗結果, 對於電平轉換 IC 的設計應用, 我們可以歸納幾點.

- 逐步移除 Device, 上升波形得以改善, 證明在設計時須考量到整段線路包含元件的容抗負載 (Capacitance Load), 當然 NVT2008 本身最大容抗負載只有到 50pF, 加上後端並聯的, 明顯已不適用此案件, 後續客戶是選用其他容抗負載支持較大的產品…

- Pull High 電阻阻值小雖然對 Over Shoot, Under Shoot 有幫助, 但在此 Case 中上升波形即使改變此處也無幫助, 反而衍生對地 Offset 增加的副作用.

- 路徑中除非特別需要串接電阻, 不然這電阻都會造成訊號驅動能力問題而導致對地 Offset 增加…

後續, 我們也會陸續分享其他應用設計的實際案例,.

大家若有興趣也可以持續關注.

最新I2C/I3C 產品型錄 :

評論