SMI:串行管理接口(Serial Management Interface),通常直接被稱為MDIO接口(Management Data Input/Output Interface)。MDIO最早在IEEE 802.3的第22卷定義,後來在第45卷又定義了增強版本的MDIO,其主要被應用於以太網的MAC和PHY層之間,用於MAC層器件通過讀寫寄存器來實現對PHY層器件的操作與管理。

MDIO主機(即產生MDC時鐘的設備)通常被稱為STA(Station Management Entity),而MDIO從機通常被稱為MMD(MDIO Management Device)。通常STA都是MAC層器件的一部分,而MMD則是PHY層器件的一部分。MDIO接口包括兩條線,MDIO和MDC,其中MDIO是雙向數據線,而MDC是由STA驅動的時鐘線。MDC時鐘的最高速率一般為2.5MHz,MDC也可以是非固定頻率,甚至可以是非週期的。MDIO接口只是會在MDC時鐘的上升沿進行採樣,而並不在意MDC時鐘的頻率(類似於I2C接口)。如下圖所示。

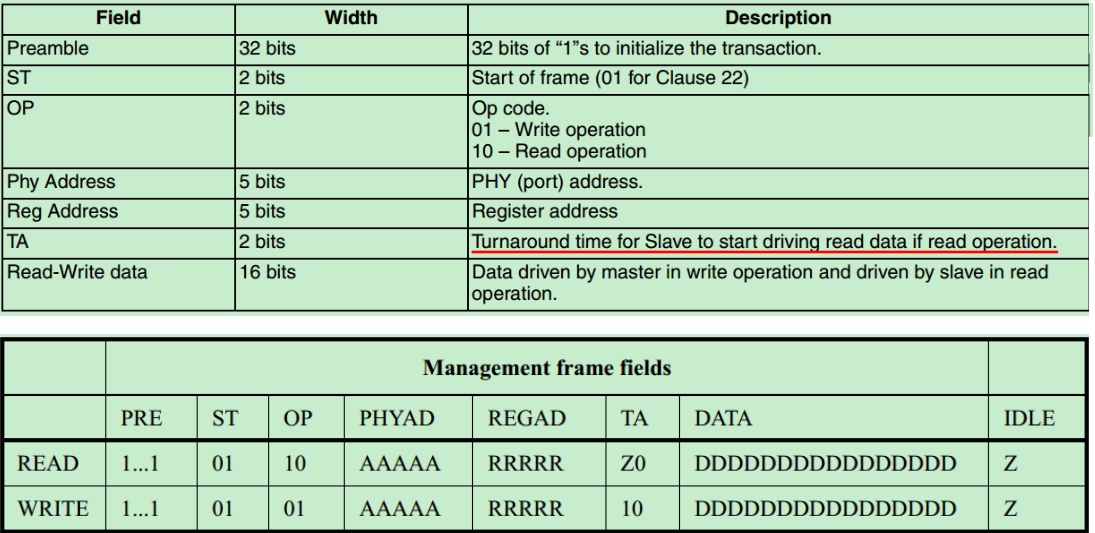

MDIO接口有兩個版本,通常被稱為卷22版本和卷45版本。卷22版本的MDIO接口最多支持連接32個MMD(PHY層設備),每個設備最多支持32個寄存器。卷45版本的MDIO接口最多支持連接32個MMD,32個設備類型,每個設備最多支持64K個寄存器。卷22版本的MDIO接口的數據幀格式如下:

具體每個bit描述如下:

卷45版本的MDIO接口的數據幀格式如下:

具體每個bit的描述如下:

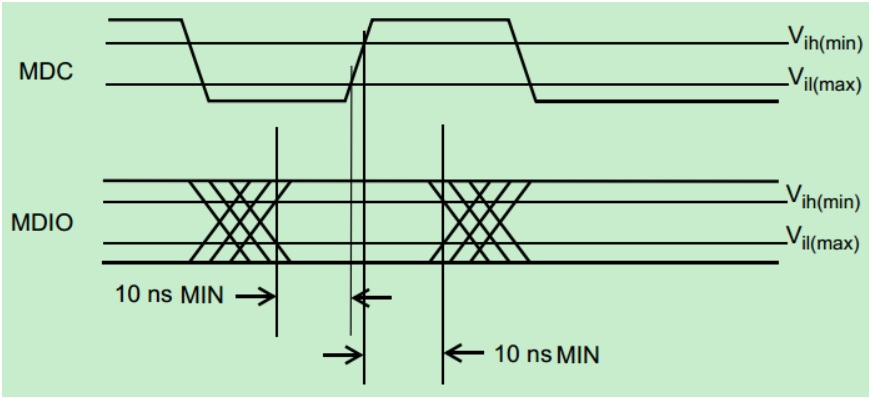

如果是STA(MAC層設備)驅動MDIO,則MDIO相對於MDC上升沿,至少要有10ns的建立時間(Setup Time)和10ns的保持時間(Hold Time)。如下圖所示:

如果MDIO是由MMD(PHY層設備)驅動的,則MDIO相對於MDC的Tco(Clock to Output Delay)的範圍是0ns~300ns。如下圖所示:

實際上,MDC的頻率也並非一定是小於或等於2.5MHz,比如Marvell的88E1512最大支持12MHz的MDC:

IEEE 802.3建議同時對MDIO進行下拉(下拉電阻建議為2k歐姆+5%),和上拉(上拉電阻建議為1.5k歐姆+5%),使得在TA時,MDIO處於中間態。但是並非所有的PHY器件都有這樣的要求,比如Marvell的88E1512只要求對MDIO進行上拉即可,上拉電阻範圍為1.5k~10kΩ。

評論