FPC Layout Suggestion ─ Cap Placement

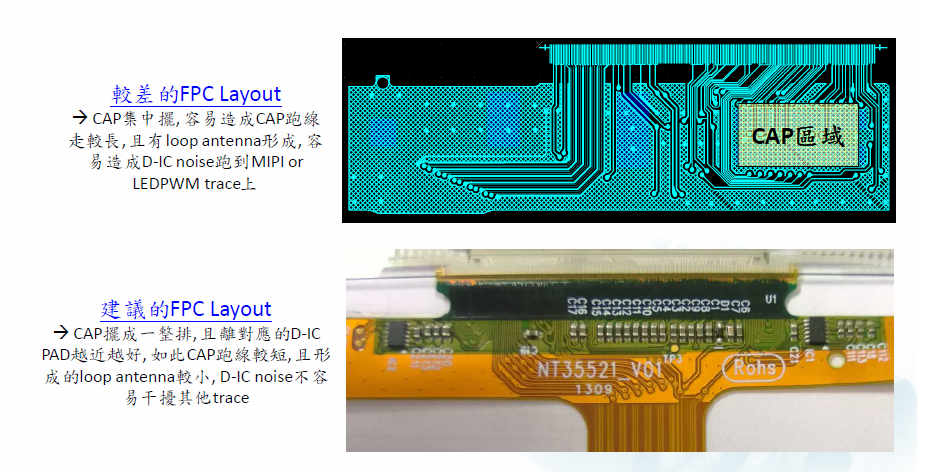

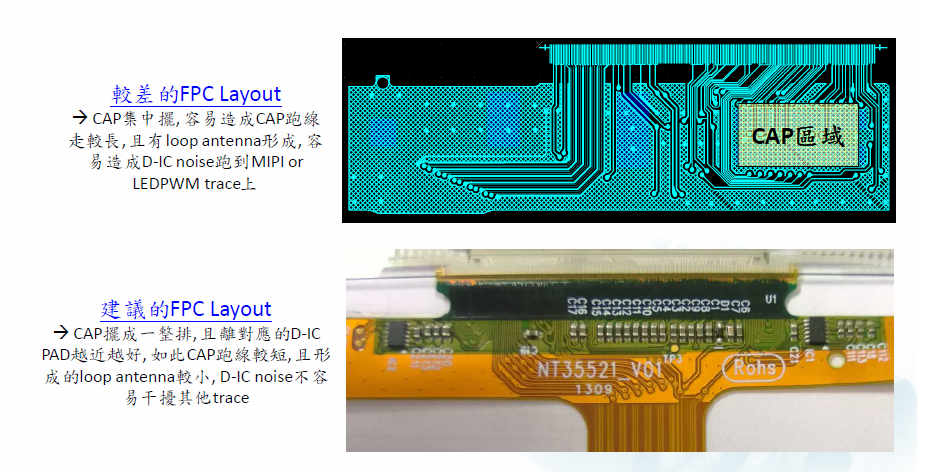

CAP Layout建議擺成一整排, 且離對應的D-IC PAD越近越好, 如此CAP跑線較短, 且形成的loop antenna較小, D-IC noise不容易干擾其他trace

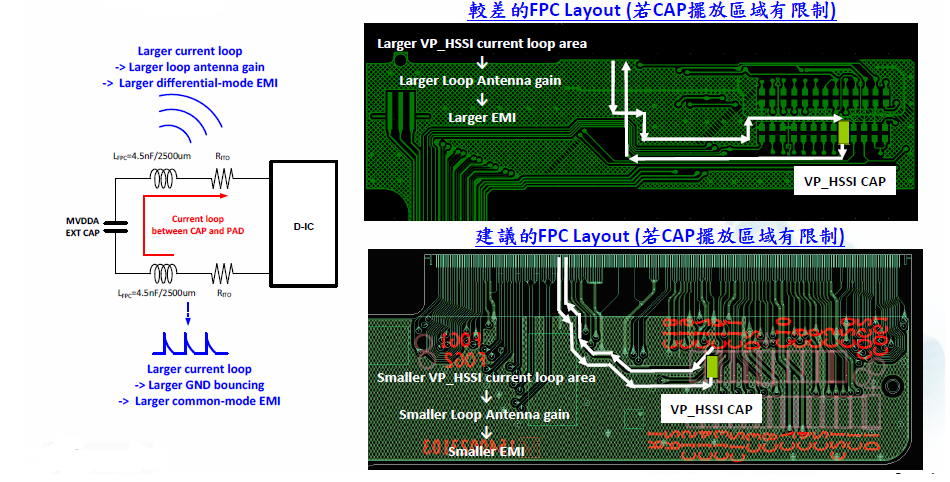

Current loop定義: D-IC電路操作會對外部CAP充放電, 而此Current會先由CAP正端流進D-IC的power PAD(如VP_HSSI), 並由D-IC對應的GND (如VG_HSSI) 循power線相鄰最近的GND流回CAP的負端, 此電流路徑就形成一個current loop. 舉下圖兩個FPC為例, 當CAP擺得越近, 且其旁邊伴隨著GND plane, 其形成的currentloop也會更小

Current Loop對EMI的影響 :由於EMI的大小正比於Current loop area及Current, 因此Current loop area越大,EMI也會越大

CAP Layout建議擺成一整排, 且離對應的D-IC PAD越近越好, 如此CAP跑線較短, 且形成的loop antenna較小, D-IC noise不容易干擾其他trace

Current loop定義: D-IC電路操作會對外部CAP充放電, 而此Current會先由CAP正端流進D-IC的power PAD(如VP_HSSI), 並由D-IC對應的GND (如VG_HSSI) 循power線相鄰最近的GND流回CAP的負端, 此電流路徑就形成一個current loop. 舉下圖兩個FPC為例, 當CAP擺得越近, 且其旁邊伴隨著GND plane, 其形成的currentloop也會更小

Current Loop對EMI的影響 :由於EMI的大小正比於Current loop area及Current, 因此Current loop area越大,EMI也會越大

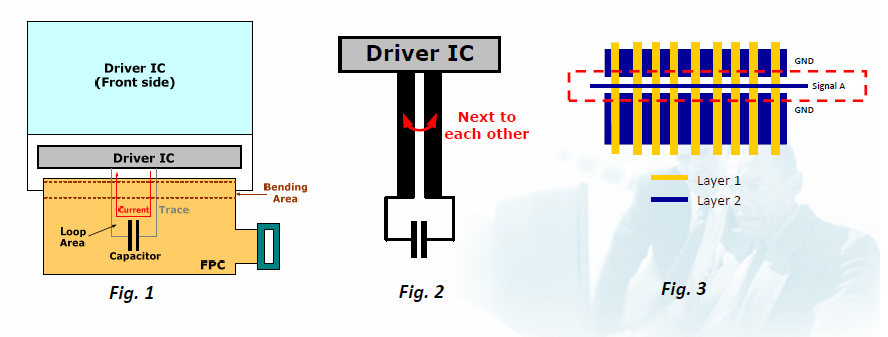

1.由於Driver IC抽電最大的電路通常是MIPI電路, 因此MIPI電路所使用到的穩壓電容(如VDD, VP_HSSI)應儘量擺放在MIPI CLK/DATA lane附近, 避免current loop面積過大, 產生過大的EMI

2.VDD/VSS這兩條走線請務必緊鄰彼此, 間距請用最小間距去減少current loop面積(Fig. 1, Fig. 2)

3.同理, VP_HSSI/VG_HSSI, C11P/C11M, C12P/C12M, C21P/C21M, C22P/C22M,這些走線請兩兩緊鄰彼此, 間距請用最小間距

4.VSS/VG_HSSI/GND走線越寬越好, 沒有走線處請都鋪滿GND, 除了MIPI trace下方的GND以外, 其餘GND請不要挖槽孔去增加GND阻抗(避免使用網狀銅)

參考來源