M031/ M032 內建逐次逼近式類比數位控制器 (SAR ADC),支持 12 位解析度,每秒可實現兩百萬次採樣 (Msps)。內建模擬多工器 (Analog Multiplexer), ADC 輸入信號可選擇從外部管腳或者內部電壓。利用 PDMA 功能,ADC 可以在沒有 CPU 參與的情況下運行,執行最大取樣速率,最小化系統電流消耗,或允許 CPU 執行其它工作專案。

完整應用筆記討論了 ADC 一般操作流程、軟硬體注意事項及 PDMA 的使用方法。最後範例程式以 PDMA 和 ADC 來展示連續採樣外部信號的流程。

概述

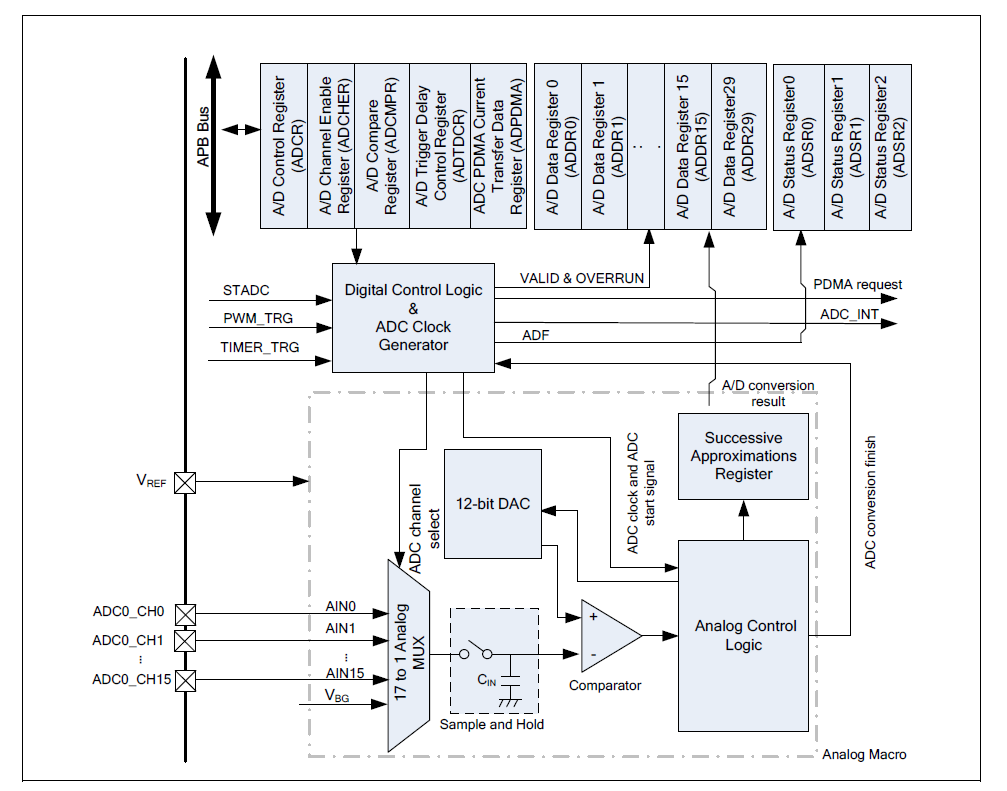

下圖說明輸入信號,參考電壓選擇和寄存器的內部連接方式,並包含以下功能:

- 一組 12 位解析度 SAR ADC 並帶獨立 VREF 管腳

- 多達 16 路的單端輸入通道或 8 組全差分模擬輸入通道

- 1 個內部輸入通道 band-gap voltage (VBG)

- A/D 轉換開始條件:

- 軟體向 ADST 位元寫1

- 外部 (STADC) 管腳觸發

- Timer 0~3 溢出脈衝觸發

- PWM 事件觸發

- 每個通道的轉換結果儲存在相應資料寄存器內,並帶有有效和覆蓋標誌

- 支援 PDMA 傳輸模式,將轉換結果儲存在使用者指定的目標位址

ADC 控制器框圖

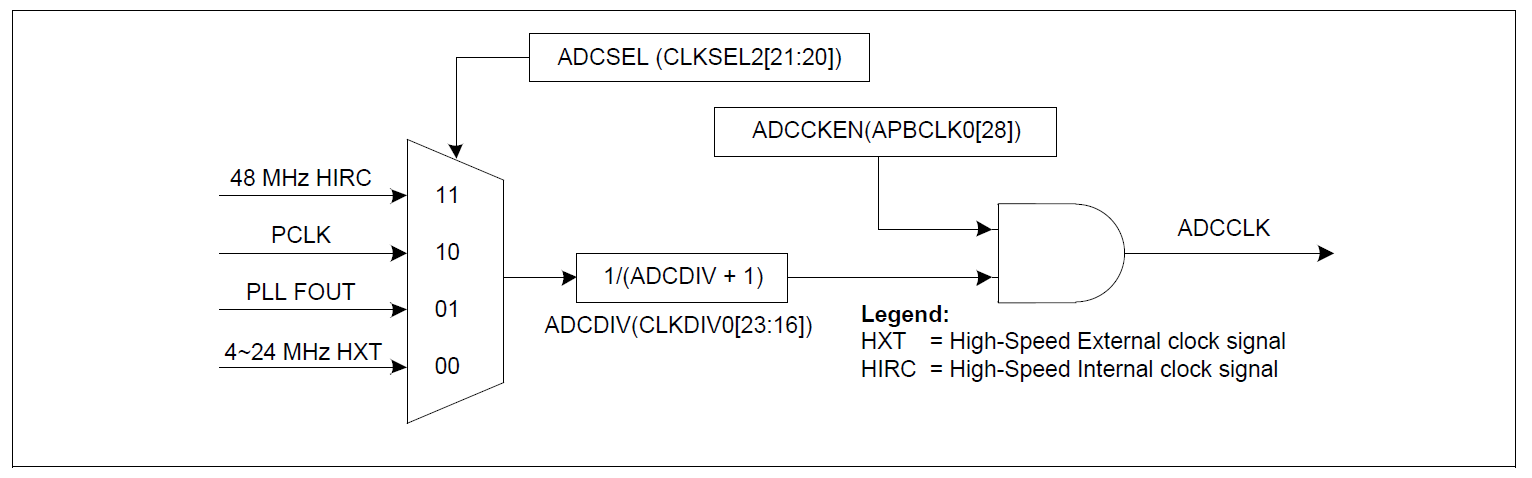

一般操作:時鐘源選擇 ADC 具有一組 8-bit 預分頻器,按照以下列公式得出 ADC 時鐘頻率 (ADCCLK) 為: ADC 時鐘頻率 (ADCCLK) = (ADC 時鐘源頻率) / (ADCDIV + 1);其中 M031/ M032 ADC 時鐘頻率 (ADCCLK) 最大值為 34 MHz。使用者可以透過 PLL 倍頻,產生 34 MHz 或者 68 MHz 頻率。將 PLL 設定為 ADC 時鐘源,並透過 ADCDIV 除頻產生 34 MHz,即可讓 ADC 運行在最高速度。

ADC 時鐘源控制

輸入模式選擇

ADC 輸入模式可以選擇為單端輸入或全差分輸入。當 DIFFEN(ADC_ADCR [10]) 為 1,ADC 為差分輸入。

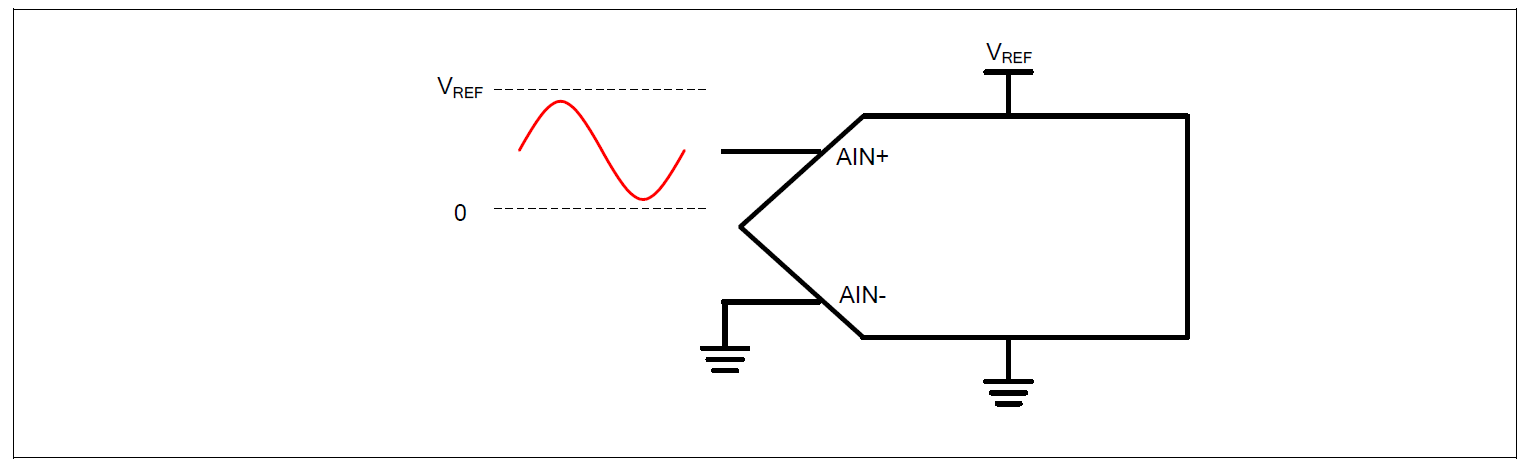

單端輸入

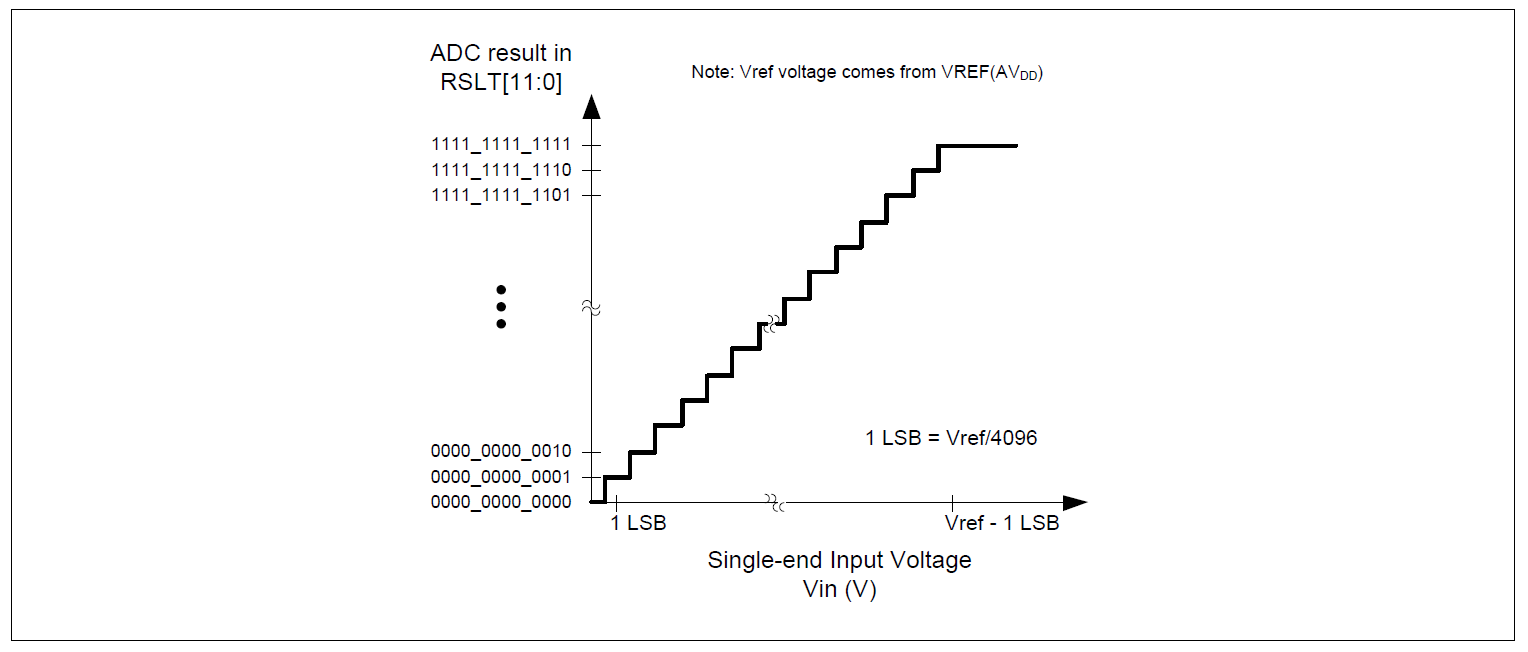

如圖「ADC 單端輸入信號」所示,在單端輸入模式下,AVSS 或者 VSS 為 ADC 負端輸入的信號 (AIN-),外部輸入電壓為 ADC 正端輸入的信號 (AIN+)。如「ADC 單端輸入模式轉換結果映射圖」所示,在 0V 和參考電壓 (VREF) 之間,切分出微小電位階。其數字結果以 0 到 4095 的無符號數,表示輸入電壓位於 0V 和參考電壓 (VREF) 之間的位置。

ADC 單端輸入信號

ADC 單端輸入模式轉換結果映射圖

全差分輸入

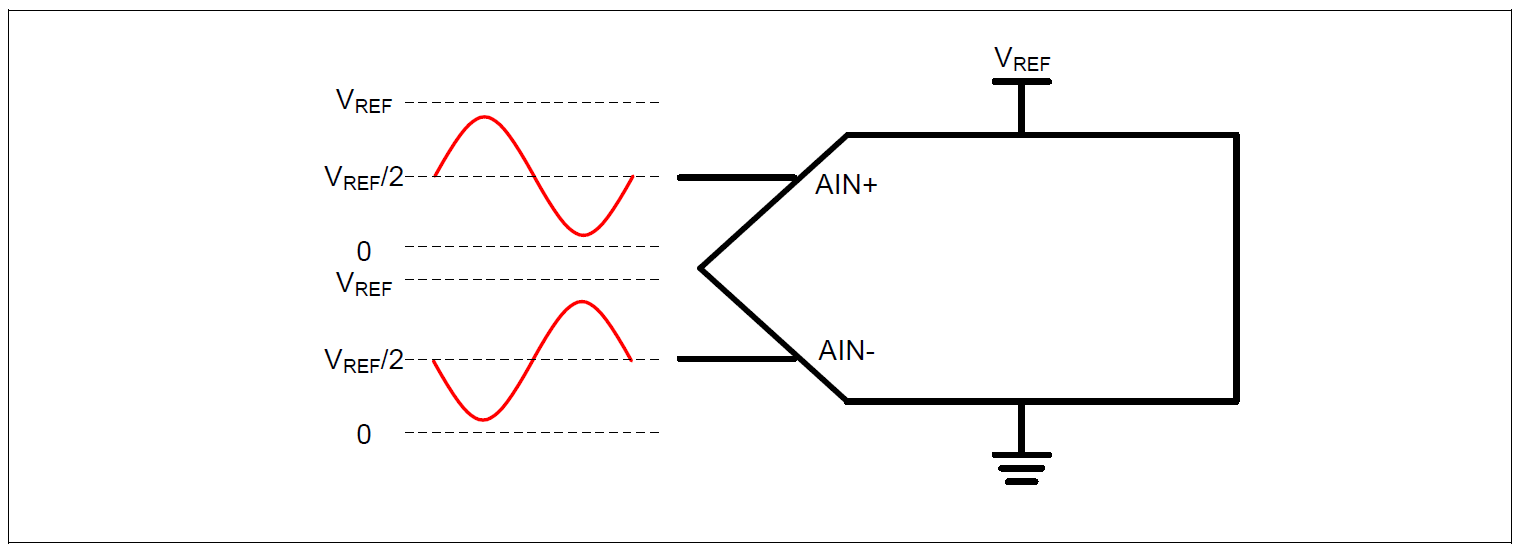

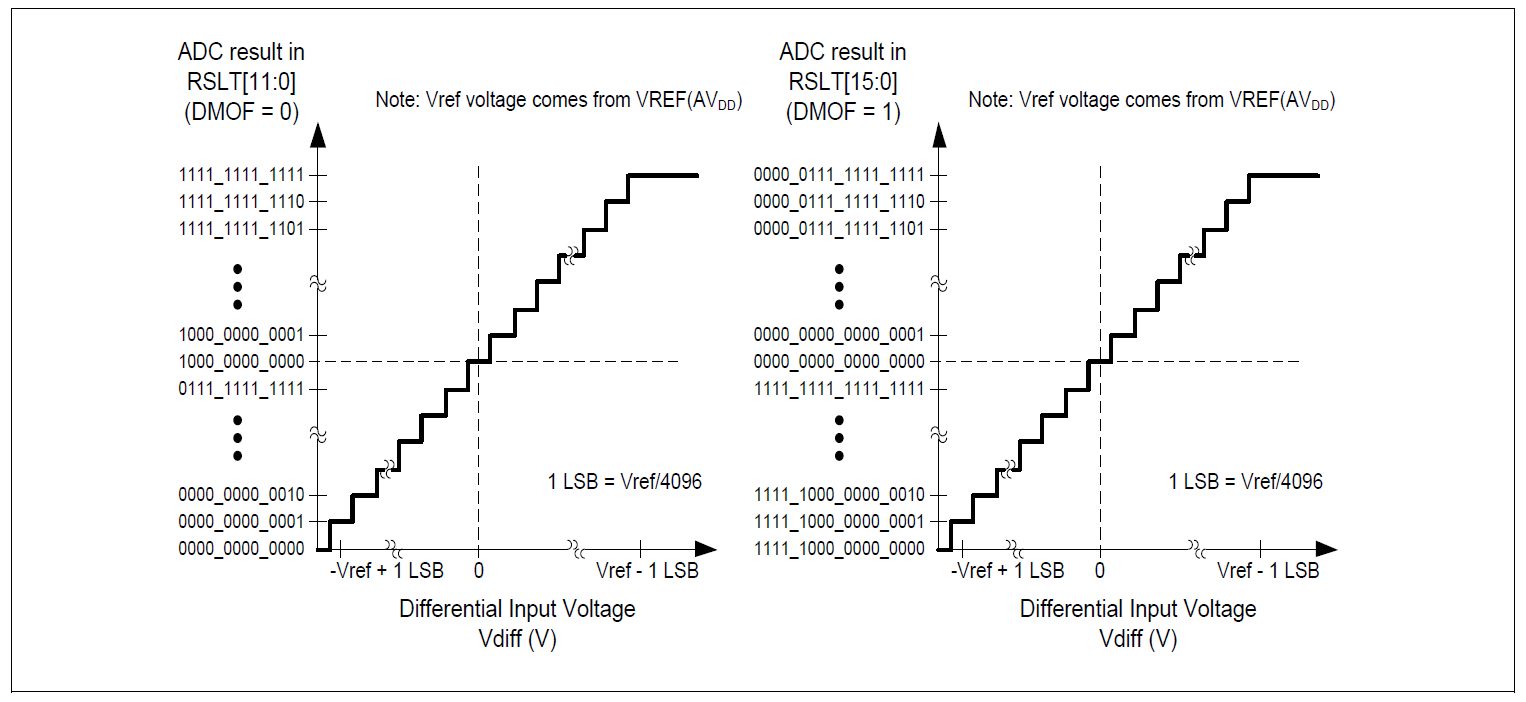

如圖「ADC 全差分輸入信號」所示,在全差分輸入模式下,測量值是兩個輸入信號之間的差值,兩個輸入信號必須為 180° 反相信號,並固定共模電壓為 VREF/2。由於一個輸入管腳被定義為正輸入管腳 (AIN+) 而另一個被定義為負輸入管腳 (AIN-),因此根據哪個輸入信號更高,差值可以是正的或負的。如「ADC 全差分輸入模式轉換結果映射圖」所示,當 DMOF(ADC_ADCR [31]) 設置為 1 時,轉換結果是以二的補數碼形式表示的有符號數,或者當 DMOF(ADC_ADCR [31]) 設置為 0 時,轉換結果是以二進位格式表示的無符號數。

ADC 全差分輸入信號

ADC 全差分輸入模式轉換結果映射圖

結論

完整的應用筆記基於應用角度,介紹類比數位轉換器的規格和特性。然後說明如何透過外部參考電壓管腳 VREF、TSMP 設定及校準,最小化 ADC 誤差並獲得最佳 ADC 精准度的方法和應用設計規則。一旦用戶掌握了這良好工作知識,就可以依照應用要求,基於速度、精准度及計算能力選擇最適合軟硬體設計參數。另外在 ADC 運行過程中,介紹利用 PDMA 快速地搬移資料或者利用數位比較器功能來偵測溫度感測器、壓力感測器及聲音感測器,減少進出 ADC 中斷次數,降低 CPU 負擔,讓 CPU 可以處理更多工。

評論