快閃記憶體通常包括NOR和NAND兩種型別。NOR快閃記憶體是由Intel公司開發的,是一種隨機訪問裝置,具有專用的地址和資料線(和SRAM類似),以位元組的方式進行讀寫,允許對儲存器當中的任何位置進行訪問,這使得NOR快閃記憶體是傳統的只讀儲存器(ROM)的一種很好的替代方案,比如計算機的BIOS晶片。而NAND快閃記憶體則沒有專用的地址線,不能直接定址,是通過一個間接的、類似I/O的介面來發送命令和地址來進行控制的,這就意味著NAND快閃記憶體只能夠以頁的方式進行訪問。相對於NOR快閃記憶體而言,NAND快閃記憶體只需要更少的邏輯閘就可以儲存相同數量的位,因此,NAND快閃記憶體比NOR快閃記憶體體積更小,儲存密度更大。就讀取速度而言,NOR快閃記憶體要比NAND快閃記憶體稍快一些;就寫入速度而言,NAND快閃記憶體要比NOR快閃記憶體快許多。NAND快閃記憶體執行擦除操作比較簡單,只需要擦除整個塊即可。NOR快閃記憶體進行擦除時,需要把所有的位都寫為1。NOR快閃記憶體雖然具備更快、更簡單的訪問過程,但是,儲存能力比較低,因此,比較適合用來進行程式的儲存。NAND快閃記憶體可以提供極高的單元儲存密度(當前單個晶片具備了32GB的儲存能力),比較適合儲存大量的資料,並且寫入和擦除的速度也很快;此外,NAND快閃記憶體的讀寫操作單元通常是一個扇區的大小(即512KB),這使得NAND快閃記憶體和磁碟的行為非常類似。

快閃記憶體晶片是由一組資料儲存單元陣列組成的,包含許多個塊,每個塊又包含許多個―頁(通常是32個頁),一個頁通常是512 位元組,因為快閃記憶體被開發出來時的最初目的就是為了取代磁碟,因此,一個快閃記憶體頁的大小和磁碟扇區大小保持了一致。一個頁不僅包括資料區域(通常是512 位元組),還包含了一個額外的、小的備用區域(通常是16 位元組),或者稱為―帶外資料(OOB:Out of Band)區域,它是用來儲存一系列的管理資訊,包括:(1)錯誤糾正碼;(2)和儲存在資料區域中的資料對應的邏輯頁面編號;(3)頁面狀態。在寫資料的同時,就可以順便把管理資訊寫入這些備用區域,額外開銷有時候可以忽略不計。每個快閃記憶體頁的狀態可以是以下三種狀態中的一種:(1)有效;(2)無效;(3)自由/擦除。當沒有資料被寫入一個頁時,這個頁就處於―擦除狀態,這時,頁中的所有位都是1。一個寫操作只能針對處於擦除狀態的頁,然後把這個頁的狀態改變為有效。異地更新會導致一些頁面不再有效,它們被稱為無效頁。 快閃記憶體的一個塊通常包含64個頁,因此,一個塊的大小通常16KB,一般稱這種快閃記憶體為―小塊NAND快閃記憶體‖。但是,一些高階應用需要更快的寫和擦除速度,因此,快閃記憶體生產商開始生產―大塊NAND快閃記憶體,這類快閃記憶體中,一個塊包含了64個頁,每個頁2112位元組,因此,一個塊的大小就是128KB。

NAND Flash作為一種比較實用的固態硬碟儲存介質,有自己的一些物理特性,需要有基本的管理技術才能使用,對設計者來說,挑戰主要在下面幾點:

1.需要先擦除才能寫入。

2.損耗機制,有耐久度限制。

3.讀寫時候造成的干擾會造成資料出錯。

4.資料的儲存期。

5.對初始和執行時候的壞塊管理。

只有至少滿足這些基本的管理技術,才能讓NAND Flash成為一款可以使用的固態儲存介質。(這裡還沒有談到任何關於效能的地方,因為那是這些基本條件滿足後的事。)

當滿足了上面的5點後,才該談到穩定,效能,耐久度,影響這些的5大因素為:

1.SLC和MLC

2.平衡磨損演算法

3.透過壞塊管理技術確保資料的完整性。

4.使用錯誤檢測和校正技術

5.寫入放大

只有滿足了這些條件,才能得到一款理想中的完美的固態硬碟。

Flash全名叫做Flash Memory,屬於非易失性儲存裝置(Non-volatile Memory Device),與此相對應的是易失性儲存裝置(Volatile Memory Device)。關於什麼是非易失性/易失性,從名字中就可以看出,非易失性就是不容易丟失,資料儲存在這類裝置中,即使斷電了,也不會丟失,這類裝置,除了Flash,還有其他比較常見的如硬碟,ROM等,與此相對的,易失性就是斷電了,資料就丟失了,比如大家常用的記憶體,不論是以前的SDRAM,DDR SDRAM,還是現在的DDR2,DDR3等,都是斷電後,資料就沒了。

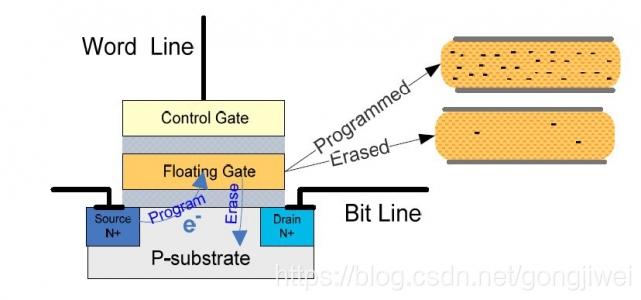

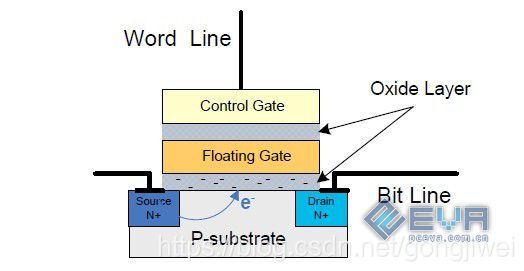

Flash的內部儲存是金屬-氧化層-半導體-場效電晶體(MOSFET),裡面有個懸浮門(Floating Gate),是真正儲存資料的單元

資料在Flash記憶體單元中是以電荷(electrical charge) 形式儲存的。儲存電荷的多少,取決於圖中的控制門(Control gate)所被施加的電壓,其控制了是向儲存單元中衝入電荷還是使其釋放電荷。而資料的表示,以所儲存的電荷的電壓是否超過一個特定的閾值Vth 來表示。

1.對於NAND Flash的寫入(程式設計),就是控制Control Gate去充電(對Control Gate加壓),使得懸浮門儲存的電荷夠多,超過閾值Vth,就表示0。

2.對於NAND Flash的擦除(Erase),就是對懸浮門放電,低於閥值Vth,就表示1。

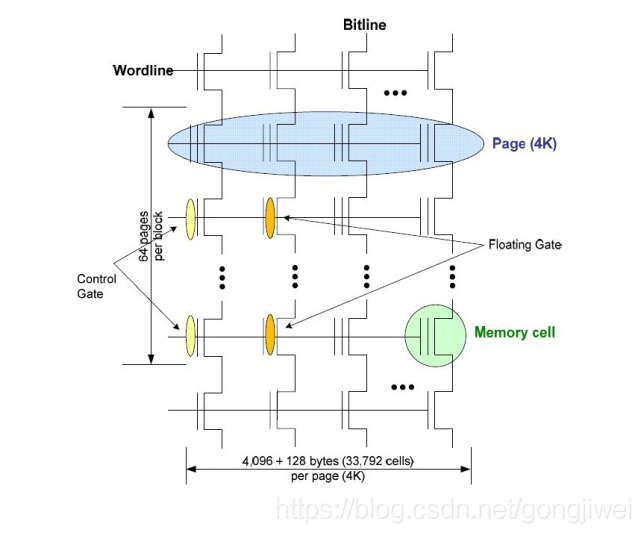

NAND Flash的架構:

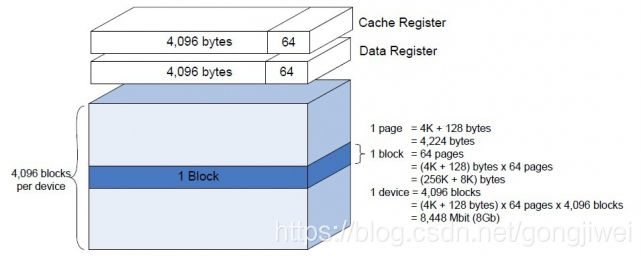

如上圖所示,這是一個8Gb 50nm的SLC顆粒內部架構。

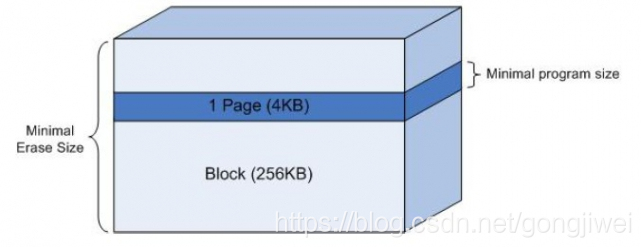

每個page有33,792個單元,每個單元代表1bit(SLC),所以每個page就是4096Byte + 128Byte。 每個Block有64個page組成,所以每個Block容量為262,114Byte + 8192Byte

page是NAND Flash上最小的讀/寫單位(一個page上的單元共享一根字元線Word line),塊是最小的擦除單位。(不同廠牌不同型號顆粒有不同的page和block大小)

下圖是個8Gb 50nm的SLC顆粒。

4KB的頁尺寸,256KB的塊尺寸。圖中4096位元組用於儲存資料,另外128位元組用來做管理和ECC用。

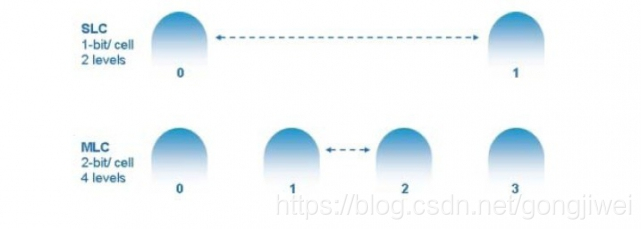

SLC 和 MLC 區別:

SLC主要針對軍工,企業級應用,有著高速寫入,低出錯率,長耐久度特性。 MLC主要針對消費級應用,有著2倍容量於SLC,低成本,適合USB閃盤,手機,數碼相機等儲存卡。如今也被用於消費級固態硬碟上。

由上圖可以看到,MLC和SLC雖然使用相同的電壓值,但是電壓之間的閥值被分成了4份,直接影響了效能和穩定性。主要有下面幾點:

1.相鄰的儲存電荷的懸浮門間會互相干擾,造成懸浮門裡的電荷不穩定出現bit錯誤,MLC由於閥值相比SLC更接近,造成出錯機率更大。 2.MLC讀寫效能降低,寫入更是降低50%以上,因為需要確認充入電荷的量,這需要更精確的處理。SLC只有0和1,也就是有和沒有,而MLC會有00,01,10,11 4個狀態,在充入電荷後還要去判斷是哪個狀態,自然就慢了。 3.因為上面說的,造成額外的讀寫壓力,所以功耗明顯增大。 4.因為額外的讀寫壓力,造成快閃記憶體的寫入耐久度和資料儲存期受到影響。

eMLC和eSLC的耐久度提升是用犧牲了資料儲存期和增加讀寫時間換來的。(也就是效能會更差點)

挑戰1:需要先擦除才能寫入。

當今的NAND Flash可以讀/寫一個page,但是必須以block大小擦除。

擦除操作就是讓塊中所有的bit變為1,從一個乾淨的“已擦除”狀態的block重新開始。當裡面的頁變為0後,只有擦除整個塊才能讓這個頁變為1。為了儘量減少擦除的次數,成熟的塊管理技術必不可少。

挑戰2:讀/寫干擾。

NAND Flash的電荷非常不穩定,在讀/寫中很容易對鄰近的單元造成干擾,干擾後會讓附近單元的電荷脫離實際的邏輯數值,造成bit出錯,因為閥值接近的關係,MLC相對SLC來說更容易受到干擾。

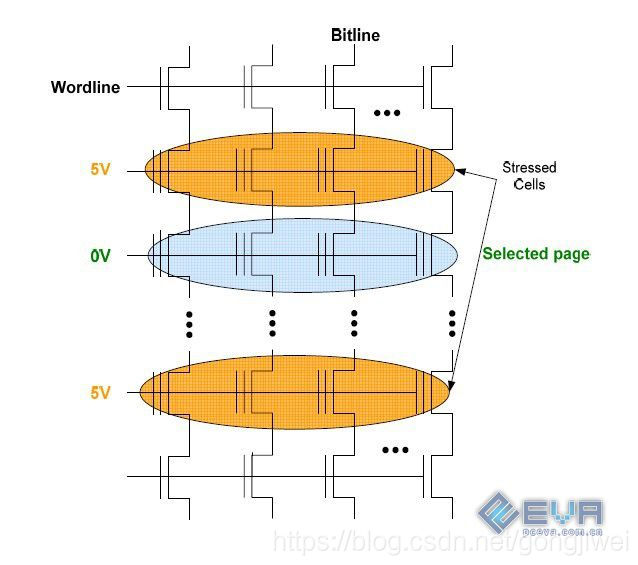

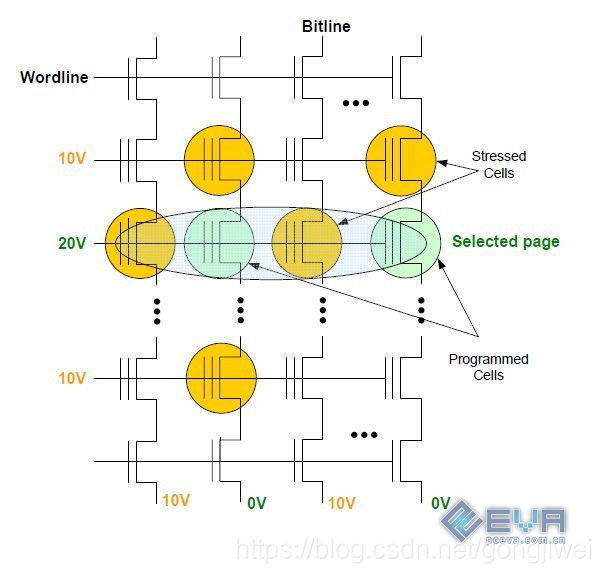

讀取干擾

讀取干擾指的是在讀取某個page時,鄰近的bit會受到升高電壓的干擾,造成bit出錯。寫入干擾指的是,某個page在寫入時,鄰近bit的電壓也被升高了,造成bit出錯。相對寫入干擾來說,讀取干擾明顯小的多。在讀/寫干擾中,可能造成某些bit被改變,結果造成資料出錯。所以需要在返回資料給主機前,用ECC/EDC演算法來糾正這些bit的錯誤。隨著快閃記憶體工藝的提升,同樣大小的晶片上被封裝入更多的單元,造成干擾越來越厲害,所以需要更強大的ECC/EDC來糾正bit。

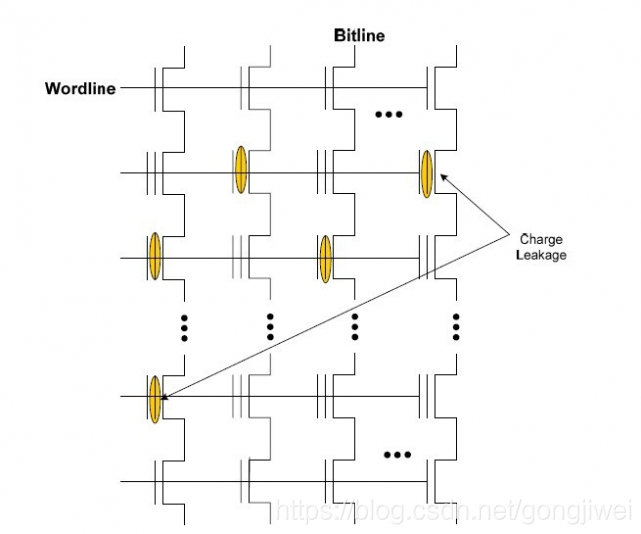

挑戰3:資料儲存期限

資料儲存期指的是當完全斷電後,資料能在NAND Flash裡儲存多久。NAND單元必須保證一個穩定的電壓水平,來保證資料是有效的。典型的SLC一般為10年。電荷從懸浮門裡漏出,我們叫做電子遷移,當隨著時間的流逝,電荷洩漏到一定程度,改變了NAND單元裡懸浮門的電壓對應的邏輯值,這樣就造成bit出錯。

資料儲存期會隨著擦寫次數的增加而明顯降低,而且從上面的原理中看出,MLC的資料儲存期明顯會比SLC少。(更容易被干擾)

挑戰4: 壞塊

NAND Flash裡有2種壞塊型別:

1,出廠壞塊:由於為了保證產量和控制成本,出廠的NAND Flash某些就會有壞塊。廠商保證SLC出廠壞塊低於2%,MLC出廠壞塊低於5%。 2,積累壞塊:在多次的寫入/擦除迴圈中,某些NAND單元的電荷電壓被永久性的改變了,那就意味著包含這個NAND單元不可用了。

所以固態硬碟需要有壞塊管理才能使用,主控制器用壞塊表來映射出廠壞塊和積累壞塊到壞塊區內,出廠時,顆粒的第一個塊Block 0廠商會保證是可用的(至少ECC後可用)。

挑戰5:擦寫次數限制

造成NAND Flash有擦寫次數限制的主要有2個因素:

1,電荷被困在氧化層,不能進入懸浮門。 2,氧化層結構被破壞。

如圖,一旦氧化層損壞到達一定程度,造成電荷越來越難在P-substrate和懸浮門之間交流。電荷被困在氧化層造成懸浮門中的電壓到不了閥值,所以說這個NAND單元就要被放入壞塊區了。

當前主流SLC的P/E為10萬次,50nm MLC為1萬次,3xnm的MLC為5000次。到了這個數字並不意味著就不能用了,這個只是代表平均壽命,也就是說到了這個次數後,壞塊就會開始大量增加了。

隨著工藝提升,ECC的要求越來越高,43nm的SLC顆粒,鎧俠規定1bit ECC的就夠了,而24nm SLC要8bit ECC, 到了1xnm MLC要求達到40bit ECC。

附; ECC

影響NAND Flash穩定性和耐久度的一個主要因素就是ECC能力,目前最常用的三種演算法是:

1.Reed-Solomon。2.Hamming。3.BCH (Bose, Ray-Chaudhuri, Hocquenghem)

不管何種ECC演算法,何種主控,檢測錯誤的方式是相同的:

1.每當一個page寫入NAND Flash,資料會通過ECC引擎,創造獨特的ECC簽名。 2.資料和對應的ECC簽名存都存放在NAND Flash裡,資料放在資料區,ECC簽名放在 SA區。 3.當需要讀取資料時,資料和ECC簽名一起被送往主控制器,此時新的ECC簽名被生成。 4.此時主控把2個簽名對照,如果簽名相同,說明資料沒有錯誤,資料就會被送往主機。如果簽名不同,資料就會先放在主控裡,而不是直接送往主機。

某些主控會把改正後的資料再次寫回快閃記憶體,另一些則不會,因為誰也不知道下次讀取會不會再出錯。

ECC的能力直接關係到NAND Flash的耐久度,資料儲存期。當NAND Flash的P/E數到了之後,錯誤數會越來越多,ECC弱的直接就報壞塊並標記退休,如果ECC能力足夠強,就能挖掘出Flash所有潛力。

評論