目的:

本應用的目的是推薦 SPI Flash 控制器和 Wibond SPI NOR Flash 設備之間的連接示意圖。

介紹:

華邦 SPI NOR Flash 設備是直接連接到 CPU/MCU/TPU 等 SPI Flash 控制器的設備。 如果有SPI Flash 以外的任何並聯元件,則必須將其包括在內進行阻抗匹配的計算。

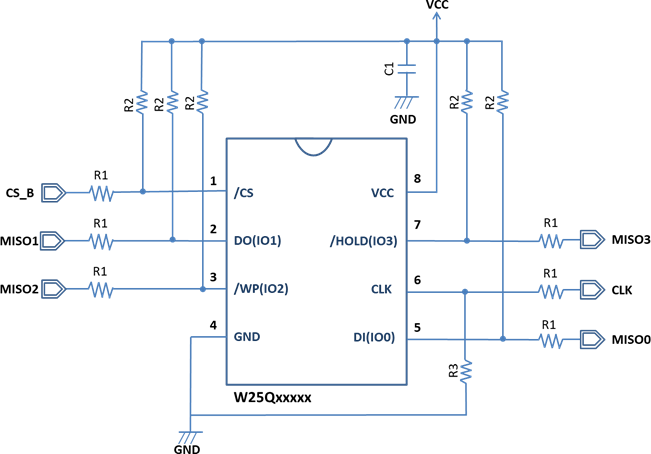

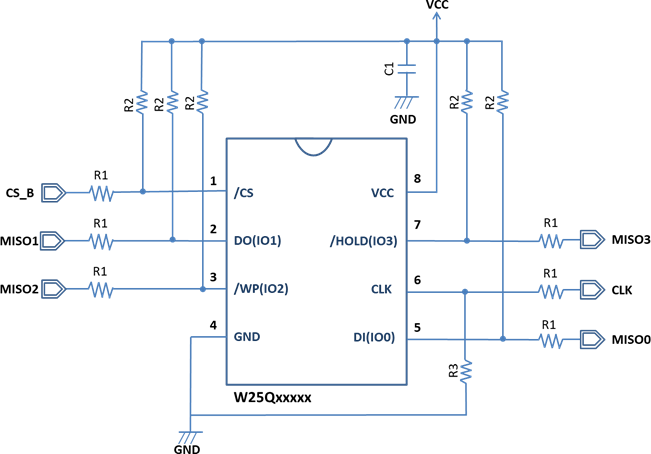

1. SPI NOR Flash 8-pin(pad) 料件推薦原理圖。

本應用的目的是推薦 SPI Flash 控制器和 Wibond SPI NOR Flash 設備之間的連接示意圖。

介紹:

華邦 SPI NOR Flash 設備是直接連接到 CPU/MCU/TPU 等 SPI Flash 控制器的設備。 如果有SPI Flash 以外的任何並聯元件,則必須將其包括在內進行阻抗匹配的計算。

1. SPI NOR Flash 8-pin(pad) 料件推薦原理圖。

|

Parameter |

Symbol |

Min |

Typ |

Max |

Unit |

Description |

|

Decoupling Capacitor |

C1 |

0.01 |

0.1 |

0.22 |

µF |

電容需要緊密連接到 Vcc 和 GND。 |

|

Data Impedance |

R1 |

45 |

50 |

55 |

Ω |

阻抗匹配以防止傳輸線中的反射雜訊 |

|

Pull-up Resistor |

R2 |

4.7 |

10 |

50 |

KΩ |

控制信號不應浮接確保防止未定義的信號狀態。 |

|

Pull-down Resistor |

R3 |

47 |

100 |

500 |

KΩ |

CLK low 將會支援Mode 0. |

2. Pull Up and Pull Down Termination Resisters.

建議:

為了防止線路的浮接,未確定的信號可以被識別為最低值。 /CS 信號低準位是可控制的狀態,/WP 信號低準位是 H/W 保護模式,/Hold 信號低準為是保持CLK訊號。許多電阻 10K-20K 是一個非常常見的數值範圍。

最大阻值:

對於電阻傳感器設計,應選擇一個與可變電阻器具相同樣為最大值的數值。但請注意如小於 1KΩ 的值,電阻可能會發熱。若大於 500KΩ 的值可能需要較長的ADC 擷取時間。

3. Decoupling or Bypass Capacitance.

建議:

用於抑制電源信號的高頻雜訊,例如當電壓漣波 overshoot/undershoot 時. 0.1μF 是低直流電源最常見的值,最大值的電容器認為是無效的,因為它們在相對較低的頻率下會產生共振頻率。所以我們不建議使用超過 10μF 的電容。

4. Exceptional cases

由於 PCB 佈局有限,如果客戶想盡量減少元件,CLK接腳的下拉電阻不是強制要使用的。

如果元件有尾碼為“Q”,則固定 Quad Enabled 料件, /Hold 功能將被使用,/Hold 引腳的上拉電阻是非必要的。

如果控制器即使在flash設備閒置狀態下也能管理所有信號的VIH/VIL,客戶不需要/CS接腳以外的所有接腳都添加上拉和下拉電阻。

8pin 以上封裝的元件可能有一個專用的/RESET 管腳,並且它內部有一個上拉電阻,因此客戶不需要為此再添加上拉電阻。

基於默認驅動程序的強度。 如果需要更改驅動能力,則需要根據 PCB 設計來優化電阻值。

參考來源