現今所有電子匯流排在大多數係統設計中都採用串列連接,時鐘時序也採用差分時鐘。差分時鐘可以傳輸更長的 PCB 走線,因為它的信號參考是它的正+和負- ,比 CMOS Clock它需要參考Vcc 或 VDD 和 GND 。 差分正+和負–時鐘在共模電壓中相互抵消,加上其相對較小的電壓擺幅,大大減少了系統時鐘的 EMI 問題。

最常用的差分時鐘是 LVPECL、LVDS、HCSL 和 CML, Diodes(達爾科技) 時鐘 IC 系列都有。本應用筆記旨在提供這些驅動程序的基本結構、解釋和實用技巧,以了解如何驅動器和接收器終端之間相互連接。

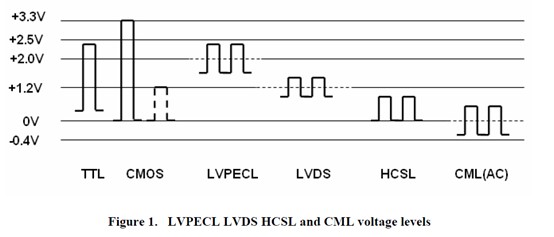

LVPECL LVDS HCSL and CML 驅動電壓

圖 1. 圖表顯示了 LVPECL、LVDS、HCSL 和 CML(AC) 電壓電平與 CMOS 時鐘的關係。 CML(AC) 是之所以列出,是因為 CML 始終用於交流耦合,其直流電壓電平與其 Vcc 電源密切相關。

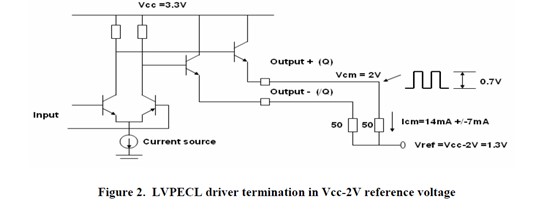

LVPECL 驅動器和終端

圖 2. 顯示了 LVPECL(Low Voltage Positive Emitter-Coupled Logic)驅動器的數據表規格圖產生大約 0.7V 擺幅差分時鐘。 單端時鐘擺幅約為 2V+/-400mV,從 +/-100mV 變化

但實際的 LVPECL 應用在接收端終端使用 150 歐姆下拉和 100 歐姆交叉,如圖3顯示,這相當於圖 2. 端接負載。 這樣,LVPECL 既可用於 DC 也可用於 AC聯軸器驅動。

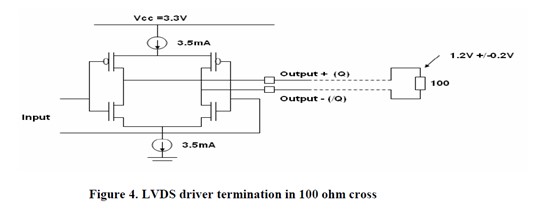

LVDS 驅動器和終端

LVDS(Low Voltage Differential Signal)驅動器是推拉驅動器,不需要下拉電阻TX 側如圖 4 所示。 它只需要 100 歐姆交叉或等效的差分終端。 這意味著耦合可以直接直流或交流耦合。

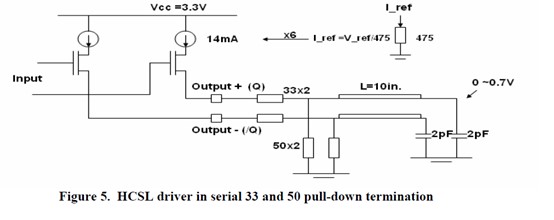

HCSL 驅動和終端

HCSL 是 Intel 為 PCIe 參考時鐘定義的差分時鐘。 它需要在串行 33 歐姆和驅動源終止50 歐姆下拉。 接收端用 2 pF 仿真驅動高阻抗終端。 信號規格為基於 10 in. +2pF 負載,如圖 5 所示。該驅動器具有 I_ref 引腳,可將 475 ohm 連接到 GND 作為驅動器參考電流。

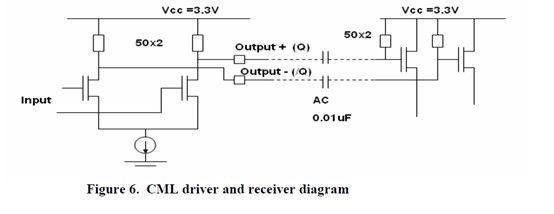

CML(Current Mode Logic)是 50 ohm 輸出驅動和 50 ohm 接收。 它在應用中使用交流耦合,例如ASIC 數據鏈路和 HDMI 都使用 CML 驅動程序。 今天更多的 ASIC 參考時鐘輸入也指定了 CML 信號輸入。 所以它的 DC 電平根據其 Vcc 電源變化,如圖 6 所示。不是那麼重要

LVPECL LVDS HCSL and CML Transformation

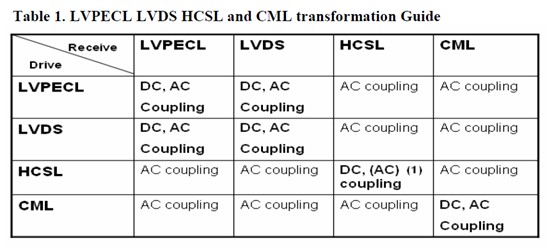

雖然這 4 種時鐘都有自己的驅動電路結構,但它們總是可以直流或交流耦合驅動,如果接收器是相同的類型。 但是實際的應用程序往往會在可用的情況下遇到它們之間的轉換終止時鐘。 下表 1. 列出了建議 AC 耦合始終為時鐘類型轉換指南的矩陣如果驅動程序和接收器不是同一類型。

值得注意的是,差分接收器始終具有不同的 Vcm(共模電壓)工作範圍,因為它差分接收時鐘,如 Pericom 大多數差分時鐘 IC 可以直接 DC 接收 LVPECL, LVDS, HCSL驅動器如數據表所示。 如果時鐘有內部偏置,則無需外部偏置電路即可接收交流驅動時鐘檢查數據表。

評論