旺宏這幾年,因各項產品積極佈局於WLCSP新製程包裝及高偕產品之原故,進而加快導入RDL製程演進的步調,從PCN文件中即可嗅出端倪。

扇出型封裝是先進封裝最具代表性的技術之一,隨著其向多晶片、3D SiP等方向發展,正越來越多地被應用在5G、AIoT和HPC等領域中。

扇出型封裝有兩大分支:

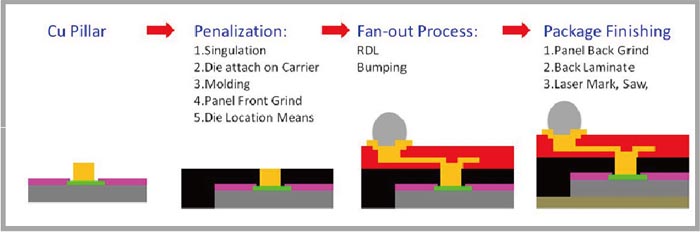

扇出型晶圓級封裝(FOWLP,下文簡稱晶圓級封裝)和扇出型板級封裝(FOPLP,下文簡稱板級封裝)。作爲後起之秀的板級封裝,由於面板的大尺寸和更高的載具使用率(95%),帶來了遠高於晶圓級封裝的規模經濟效益。而作爲其核心的RDL(Redistribution Layer,重佈線層)技術,也得到了業界更多的關注。

什麼是 RDL重分佈線路製程

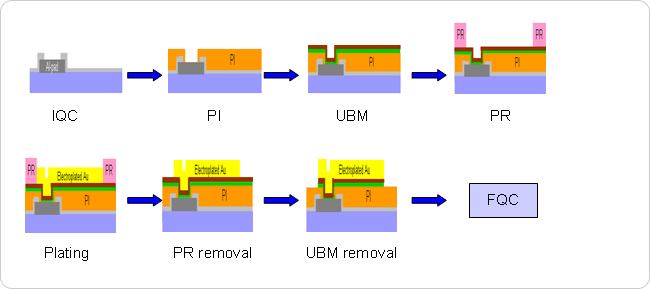

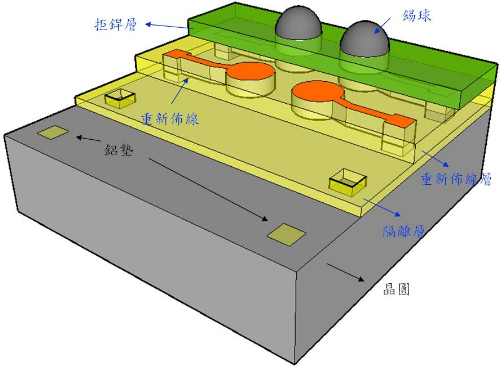

重分佈製程(RDL)是將原設計的IC線路接點位置(I/O pad),透過晶圓級金屬佈線製程和凸塊製程來改變其接點位置,使IC能應用於不同的元件模組。重新分佈的金屬線路如果是以金(Au)材料為主,則稱為金線路重分佈(Au-RDL)。

所謂的晶圓級金屬佈線製程,是先在IC上塗佈一層保護層,再以曝光顯影的方式定義新的導線圖案,接下來再利用電鍍和蝕刻技術製作新的金屬導線,以連結原鋁墊(Al pad)和新的金墊(Au pad)或凸塊(bump),達到線路重新分佈的目的。

RDL有什麼特點

1. 改變線路I/O原有設計,增加原有設計的附加價值。

2. 加大I/O的間距,提供較大的凸塊面積,降低基板與元件間的應力,增加元件的可靠性。

3. 取代部分IC線路設計,加速IC開發時程。

RDL產品應用面

電源管理晶片 (Power IC);磁耦合器 (magnetic coupler);

磁感應、雜訊除去;高速同步動態記隨機存取記憶體元件 (High speed DDR SDRAM);

高頻電感元件;壓力感測元件; Wireless (RF, TV)RF PA, RF LNA, RF Transceiver 等。

承上啟下的RDL 為重要橋樑

板級封裝借鋻了晶圓級封裝的思路和技術,但採用了更大的面板,因此可以量産出數倍於大尺寸晶圓晶片的封裝産品。而且,其基板選材更加霛活,可以採用液晶面板用的玻璃基板或是安定性較佳的金屬基板。

在發展晶圓級封裝的時候,有人想到既然可以在晶圓上面直接做封裝,如果把晶圓換成面板,用面板的設備也可以做同樣的事情,於是就開發出了板級封裝。

與晶圓級封裝相同,板級封裝可以將封裝前後段制程整合進行,可以被眡爲完整的封裝制程,因此可大幅降低生産與材料等各項成本。擧例而言,板級封裝採用了如24×18英寸(610×457mm)的PCB載板,其面積大約是12英寸晶圓的4倍,就相當於一次制程下可以量産出4倍於12英寸晶圓的封裝産品。巨大的成本優勢促使了全球各大封裝業者的加入,三星機電、日月光等均積極投入到板級封裝制程技術中。

板級封裝與晶圓級封裝各有擅長,CPU、GPU、FPGA等大型晶片多用晶圓級封裝,APE、PMIC等主要以板級封裝爲主。不過,通過RDL技術將不同的晶片整合在單一封裝體中,可以使板級封裝實現更細線寬線距,達到與晶圓級封裝相同的效果。

高精密設備制造商Manz亞智科技技術処長李裕正表示,印刷電路板最小的線寬尺寸大概可以做到35μm,但是在IC制造方面來講已經到5nm,在晶片面積不斷微縮的情況下,要實現晶片與PCB板的連接,就必須有一些互聯的技術來彌補兩者的差距,RDL技術就是其中之一。

RDL技術的核心是在晶圓表面沉積金屬層和介質層並形成相應的金屬佈線圖形,來對晶片的 I/O 端口進行重新佈局,將其佈置到新的、節距佔位可更爲寬松的區域。能制作高品質的精細線路是RDL的強項。李裕正指出,IC載板在發展精細線路上的良率很低,但是RDL工藝制作的線寬符合晶圓和板級封裝1~10μm之間的範圍。同時,RDL層使用了高分子聚合物(Polymer)爲基礎的薄膜材料來制作,可以取代矽中介層跟封裝載板,不僅省下大量成本,也讓晶片的封裝厚度明顯降低。

故多數大廠及IC設計公司,在近幾年間大量的進行RDL製程演進,也發行為數不少的PCN文件通知終端客戶許多QE級QC紛紛不知所措,何為RDL製程演進,此篇就能讓大家更理解此製程的關鍵之處。

參考來源