概述:

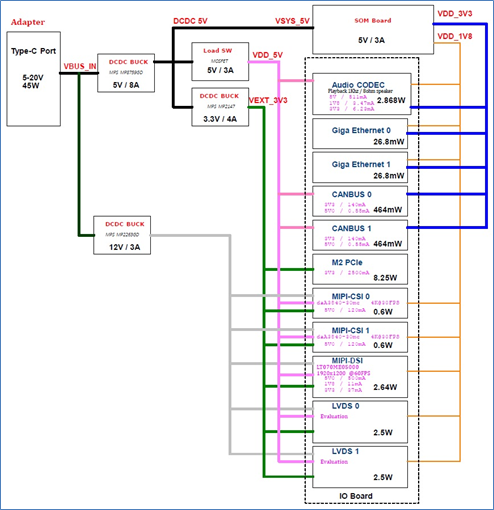

本文主要介紹恩智浦 i.MX8M Plus 硬體設計須知,並將此晶片設計成 OP-Killer EVM 方案,並提供方案功能,SOM Board 方塊圖、IO Board 方塊圖、

SOM Board 電源架構圖、IO Board 電源架構圖、硬體設計指南,讓讀者能按照此份文件,能更快熟悉 i.MX8M Plus 硬體設計規則。

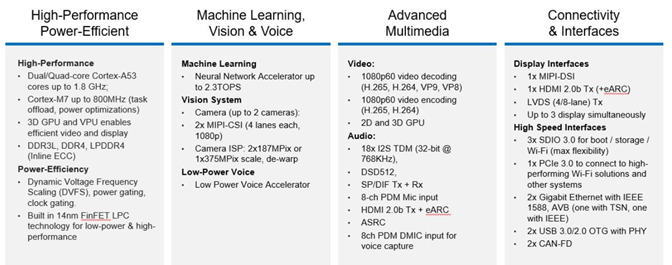

一、主要功能:

二、功能描述:

- SOM Board Support:

- Micro SD card

- NOR

- FlasheMMC 5.1

- Peripherals Support:

- USB 3.0 ( Type C ) x 1,USB 3.0 x 1 ( OTG )

- HDMI 2.0 Output x 1,MIPI-DSI x 1,LVDS ( 2 Channel ) x 1

- Gigabit Ethernet x 2 ( TSN x 1 )

- Debug Port ( Micro USB 2.0 ) x 1

- MIPI - CSI x 2

- PCIe M2 Connector x 1

- GPIO & I2C Extend Connector x 1

- MIC Input x 2,Audio Output x 1 ( Option )

- Expansion Connector x 1

- WIFI 6 & BT 5.2 Module ( Option )

三、線路圖

1-1方塊圖:

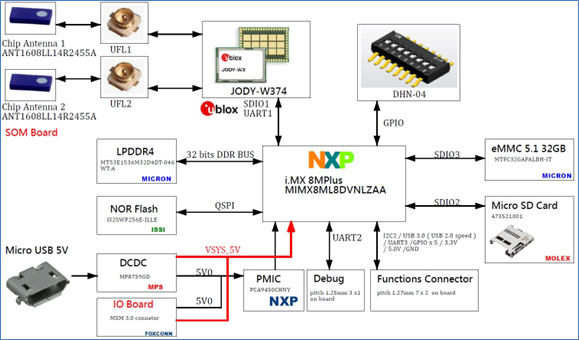

1-1-1 SOM Board 方塊圖:

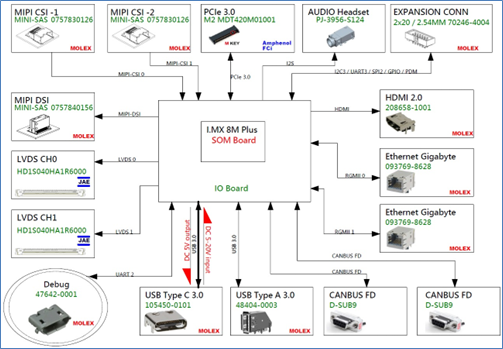

1-1-2 IO Board 方塊圖:

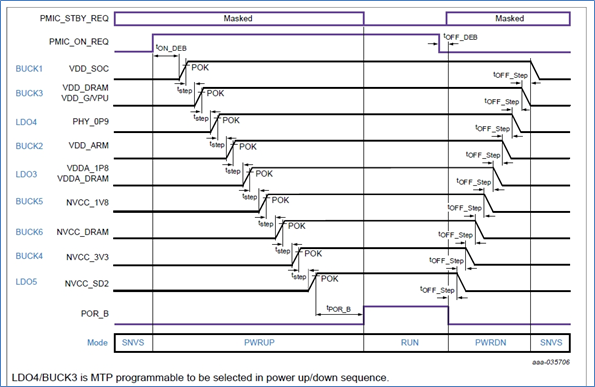

1-2 電源架構圖:

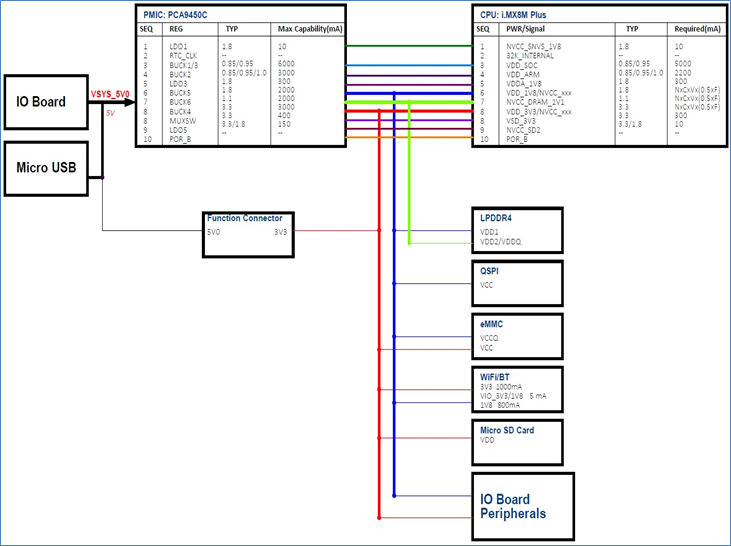

1-2-1 SOM Board 電源架構圖:

1-2-2 IO Board 電源架構圖:

1-3 SOM Board 與 IO Board 線路:

線路圖索取資料請與我們聯繫 Atu.tw@wpi-group.com

四、i.MX8M PLUS 硬體設計指南:

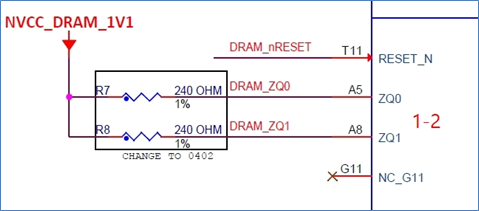

1-1 LPDDR4:

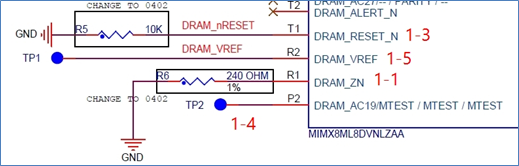

1-1-1. R1 Ball DRAM_ZN 腳位需連接 240Ω ( 1% ) 電阻至 GND

1-1-2. A5 ( ZQ0 ) & ZQ1 ( A8 ) 腳位需連接 240Ω ( 1% ) 電阻至 DRAM Power VDD

1-1-3. T1 Ball DRAM_RESET 腳位需連接 10KΩ ( 5% ) 電阻至 GND

1-1-4. P2 Ball MTEST 腳位應預留測點,並使其 Floating

1-1-5. R2 Ball VREF 腳位應預留測點,並使其 Floating

1-2 I2C:

1-2-1 不同速率的 I2C 接口,請務必分開,快速一組,低速一組 (ex: 快速 400 Kbits ,慢速 100 Kbits)

1-2-2 如果 I2C 接口位址有衝突,可使用 PCA9646 I2C 開關控制切換

1-2-3 避免在同組 I2C 接口上,加上多組 Pull-High 電阻,避免負載異常

1-2-4 I2C Pull-High 電源,要與 CPU 電源使用同一組,避免電源時序不同,導致電源倒灌

1-3 JTAG:

1-3-1 JTAG_TDO 請勿 Pull-High & Pull-Low,並使其 Floating

1-3-2 G20 Ball JTAG_MOD Normal Mode 腳位需 Pull-Down 10KΩ,Boundary-Scan Mode 腳位需 Pull-up 2.2KΩ 連接至 JTAG_VCC

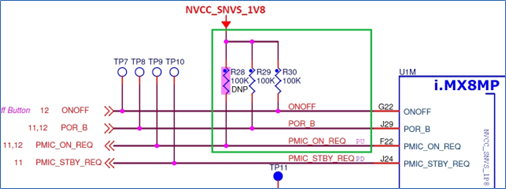

1-4 Reset & ON/OFF:

1-4-1 POR_B Ball J29 腳位需連接 100KΩ ( 5% ) 電阻至 SNVS_1V8 ON / OFF Ball G22 腳位需連接 100KΩ ( 5% ) 電阻至 SNVS_1V8,可透過軟體設定切換模式,

並設置斷電時間 ( EX:長壓 ON/OFF KEY 5 Sec ),PMIC_ON_REQ F22 腳位需連接 100KΩ ( 5% ) 電阻至 SNVS_1V8

1-4-2 WDOG_B Ball B6 腳位需連接 100KΩ ( 5% ) 電阻至 SNVS_1V8 ,Active Low 重置 PMIC ( 電源重置 )

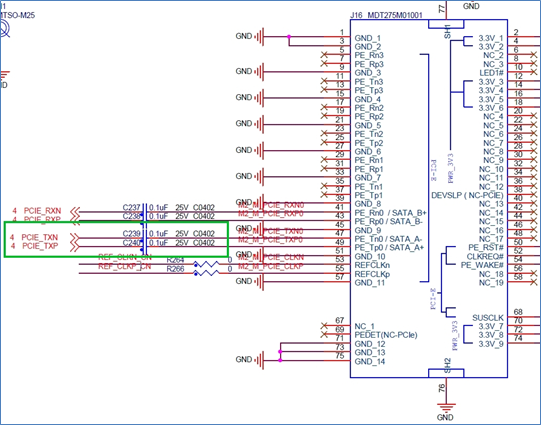

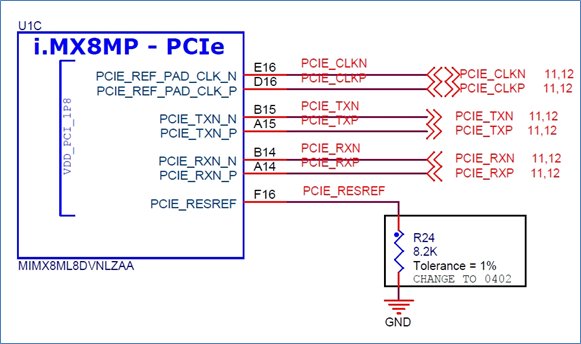

1-5 PCIe:

1-5-1 PCIE_TXN_N Ball B15 腳位需在 Device 端串聯 0.1uF 電容,使其轉為直流訊號 PCIE_TXN_P Ball A15 腳位需在 Device 端串聯 0.1uF 電容,

使其轉為直流訊號

1-5-2 PCIE_RESREF Ball F16 腳位需連接 8.2KΩ ( 1% ) 電阻至 GND

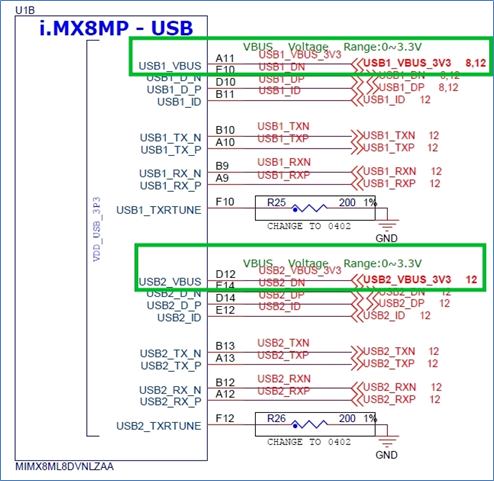

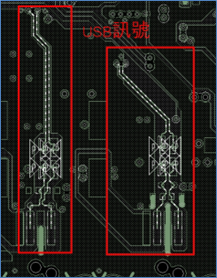

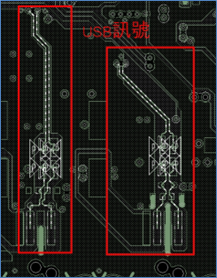

1-6 USB:

1-6-1 USB1_TXRTUNE Ball F10 腳位需連接 200Ω ( 1% ) 電阻至 GND

USB2_TXRTUNE Ball F12 腳位需連接 200Ω ( 1% ) 電阻至 GND

1-6-2 USB為 Differential Signals,需走阻抗匹配 90Ω

1-6-3 USB ESD 選用,選用 Low capacitance 的元件,以防止干擾 USB 高速訊號

1-6-4 USB1_VBUS Ball A11 腳位可承受電壓範圍 0V~3.3 V

USB2_VBUS Ball D12 腳位可承受電壓範圍 0V~3.3 V

1-6-5 USB3.0 TX/RX PCB Trace 避免超過 6 inches , 以免無法通過 Eye Pattern

1-7 FlexSPI:

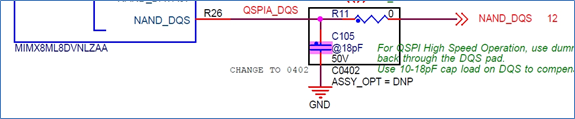

1-7-1 NAND_DQS Ball R26 腳位連接 10~18 pF 電容至 GND,補償 SIO/SCK 高速負載

1-8 Oscillator/ Crystal 注意事項:

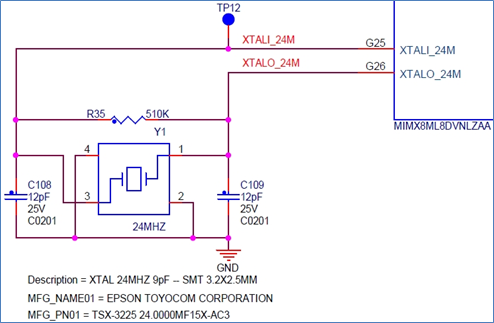

1-8-1 24M_XTALI ( Balls G25 ) 和 24M_XTALO ( ball G26 ) 需並接電阻 510KΩ ( 1% ) 電阻,並注意選用的晶體 ESR 需小於 60Ω,額定驅動不得小於 100 uW

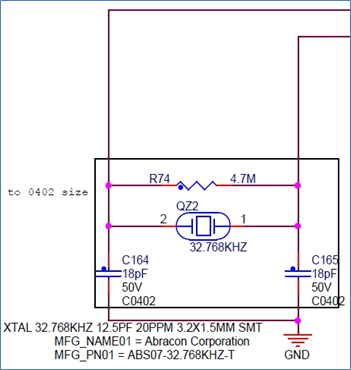

1-8-2 RTC_XTALI ( Ball J25 ) 和 RTC_XTALO ( ball J26 ) 需並接電阻 4.7MΩ ( 1% ) 電阻,並注意選用的晶體 ESR 需小於 70KΩ,額定驅動不得小於 0.5 uW

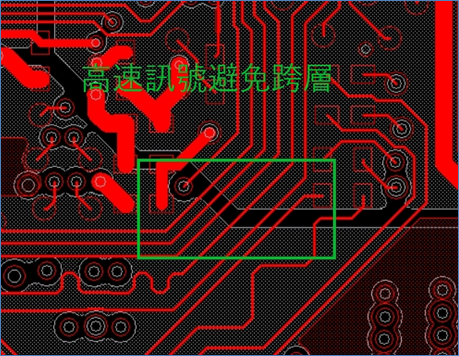

1-9 PCB Design:

1-9-1. 高速訊號對應的參考層請選擇 GND,以確保訊號完整性

1-9-2. 高速訊號避免跨層,導致訊號 crosstalk

1-9-3. DDR 的 Layout 請參考 EVK,可直接複製使用

1-9-4. DDR 上的 TP 點,直徑不可超過 20mil,請直接加在走線上

1-9-5. Decoupling Cap 請靠近 IC Power 腳位

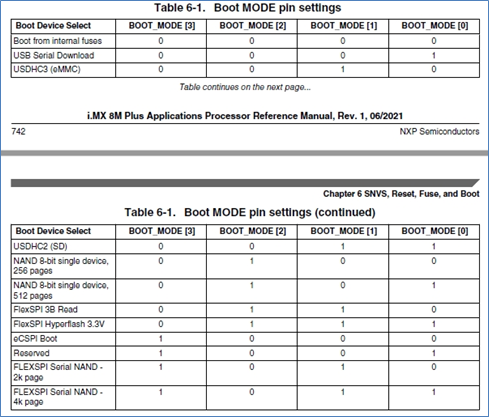

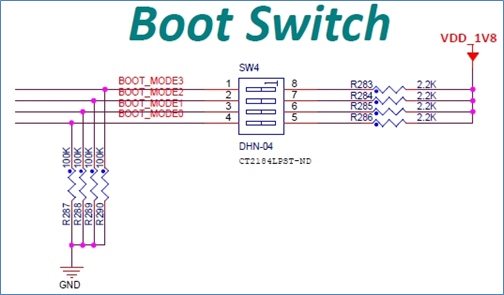

1-10 Boot Mode:

1-10-1. i.MX8M Plus Boot Mode : 參考 IMX8MPRM.pdf 6.1.2.1 Boot mode pin settings,並預留 Pull High or Pull Low 電阻

Mode Table

Boot Switch

以上為 OP-Killer (i.MX8M Plus) 方案介紹與設計須知,WPI 將設計的過程濃縮成此篇博文,希望能藉此幫助讀者更快的進入 i.MX8M Plus 的世界,並且設計出屬於自己的 i.MX8M Plus 系統。

如果各位讀者有任何問題,可以在下面留言一起討論喔 ! 謝謝。

參考文件:

參考來源