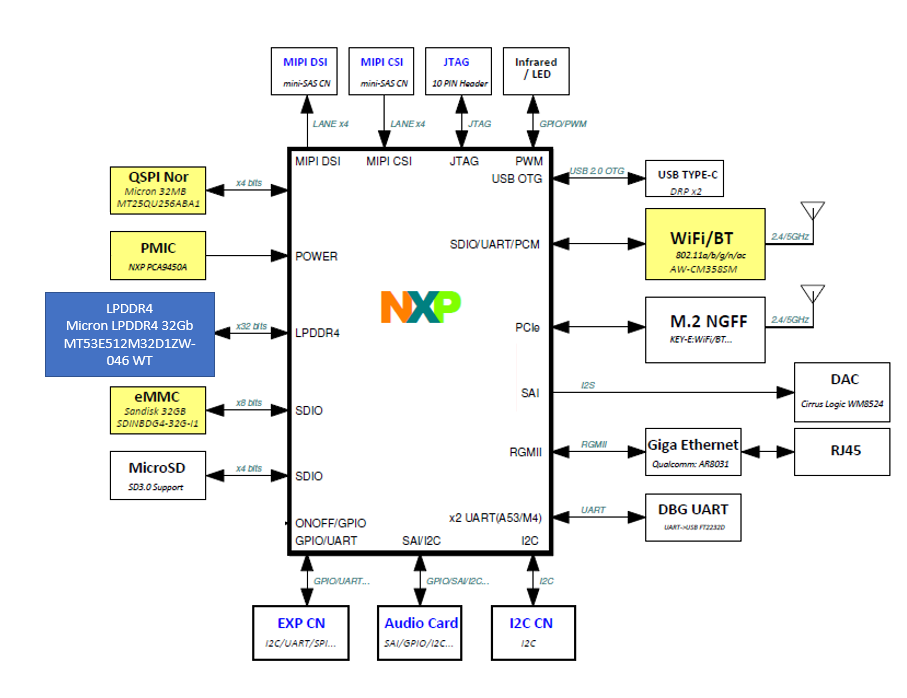

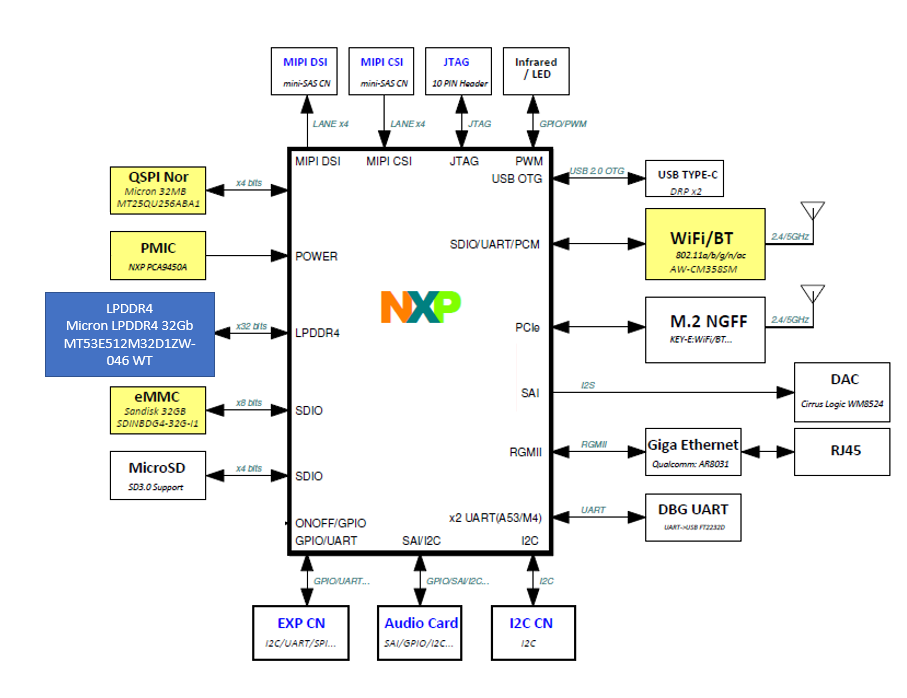

1. 搭配 iMX8M Mini processor 對於 Micron LPDDR4 32Gb (Z42M) 1 -alpha process 相容性訊號量測.

證實Micron LPDDR4 新製程 1 -alpha相容於 iMX8M platform.

2. DDR系統屬於高速 interface 。因此,為了確保Host與DRAM之間的信號能正確傳輸,JEDEC針對各種信號(例如CLK、C/A、DQ、DQS)在時序、形狀等方面進行了細緻的規範。

通常認為,滿足這些規範是DDR interface 能夠正確運行的最低要求。如果希望系統在復雜多變的環境中能夠保持良好的穩健性,則常常需要在滿足底限要求的基礎上額外預留一些裕量(Margin)。

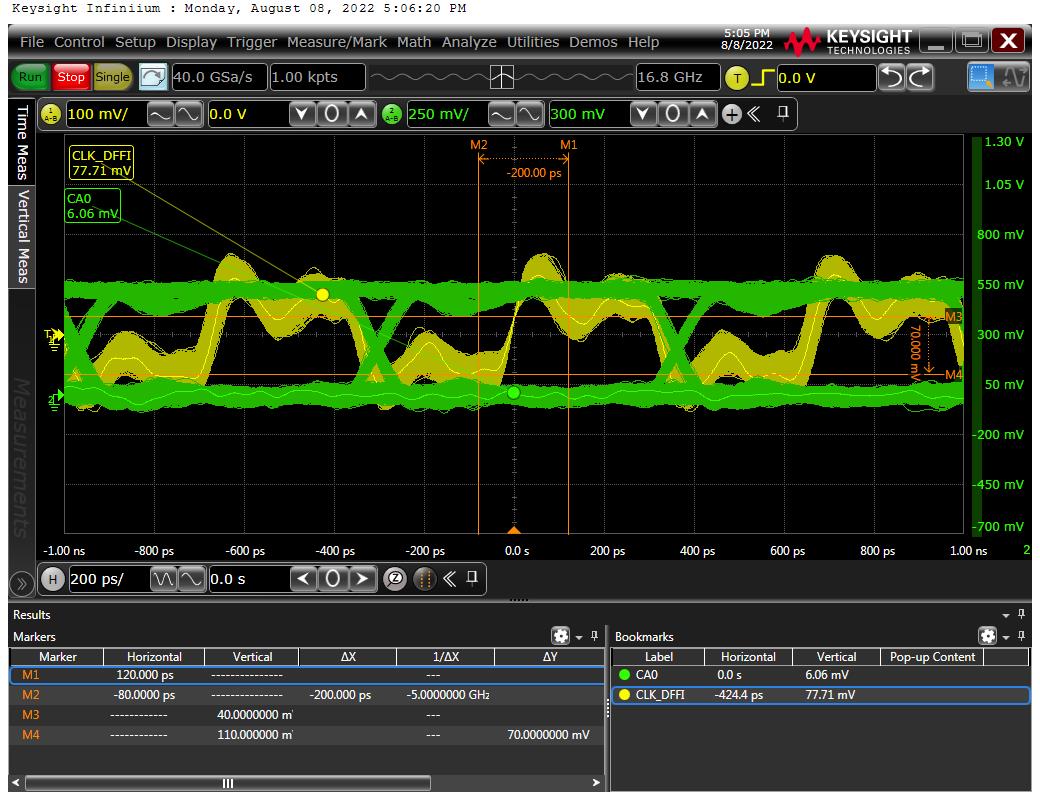

下圖展示的是在Interposer的Probing Pad上測量得到的LPDDR4X的眼圖(為CA,為CK)。可以看到,波形存在明顯畸變,這是因為在測量點處不但有來自SOC的入射波,

證實Micron LPDDR4 新製程 1 -alpha相容於 iMX8M platform.

2. DDR系統屬於高速 interface 。因此,為了確保Host與DRAM之間的信號能正確傳輸,JEDEC針對各種信號(例如CLK、C/A、DQ、DQS)在時序、形狀等方面進行了細緻的規範。

通常認為,滿足這些規範是DDR interface 能夠正確運行的最低要求。如果希望系統在復雜多變的環境中能夠保持良好的穩健性,則常常需要在滿足底限要求的基礎上額外預留一些裕量(Margin)。

下圖展示的是在Interposer的Probing Pad上測量得到的LPDDR4X的眼圖(為CA,為CK)。可以看到,波形存在明顯畸變,這是因為在測量點處不但有來自SOC的入射波,

還有來自DRAM的反射波(由於Cio、CA分支結構、Bonding-wire寄生電感等導致阻抗不匹配,從而引起反射)。

測得的波形實際上是二者的疊加,因此並不能準確反映DRAM接收端看到的波形。

評論