SiC FET的導通阻抗Rds-on值會受到不同Vgs電壓的影響。在相同的溫度條件下,較高的SiC FET Vgs電壓會有較低的Rds-on值,可以進一步減少conduction loss,

因此在效率的表現上也會比較好。Infineon的SiC FET在Vgs建議電壓設計為15V~18V之間。

Infineon的SiC FET在Vgs電壓關斷時,並不需要負壓來截止,只需維持在當Vgs=0V即可。因為太深的Vgs負壓,會導致Vgs,th產生偏移,讓Rds-on增加,

進而讓效率與溫度變差,進而影響到整體PSU的產品壽命。但為了考量到與其它競爭者的共用性問題,建議Vgs負壓控制在-2V以內。SiC FET對負壓的耐受

度為當Vgs=-2.5V可承受時間為30ns,而當Vgs=-5V可承受時間為15ns,Vgs,peak則為-7.5V

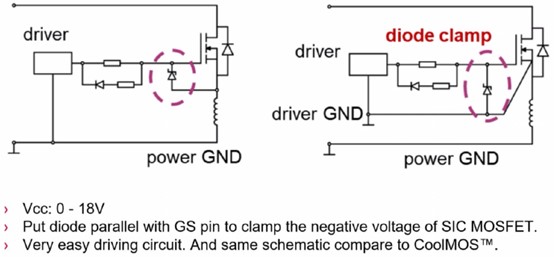

雖然SiC FET的Vgs對負壓有一定程度的耐受度,但Infineon仍建議在MOSFET G到S端之間並一diode來做為負壓的鉗制,對於負壓會有很好的的抑制效果。

SiC FET在SOA的曲線上幾乎呈現與silicon MOSFET一致的情形。在較短時交越時間條件下,則可以承受較高的電流,差別只在silicon MOSFET在Rds-on比較大。

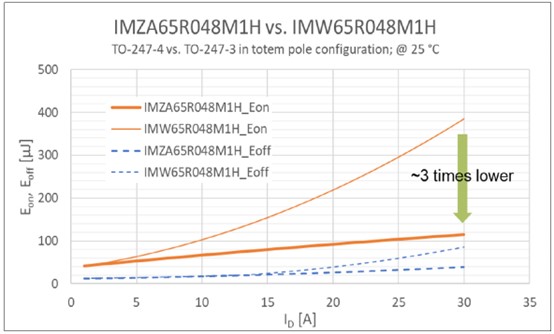

SiC FET在封裝的選用上建議儘可能選用TO247-4pin封裝,因其具有driver source pin,可以幫助減少Eon與Eoff的power loss,特別是在重載的條件下,

對提升效率有很大的幫助。

產品總結:

由於SiC FET的產品具有很好的溫度特性,因此非常適合設計在大功率產品的設計與應用,同時各個供應商皆有相對應的包裝與相同的腳pin定義,不需要去

擔心替代料的來源與供貨短缺的問題。

參考來源