摘要:

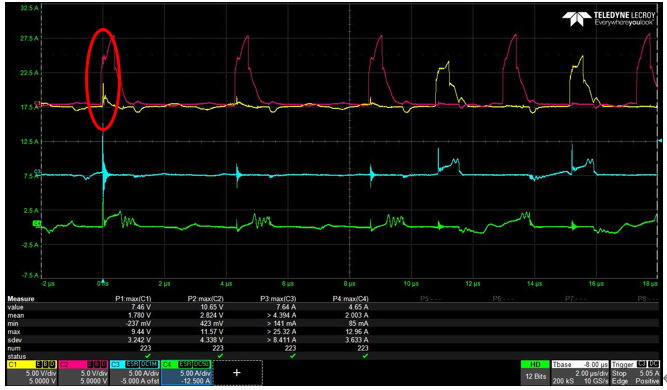

在一些非穩態的情況下,Vgs有可能因為雜訊干擾、電路特性等成因產生瞬間大突波。這時候往往會擔心,到底Vgs突波會不會導致開關誤動作,而產生short through現象,如圖一所示。

實際上Vgs並非有電就會有產生導通現象,而是需要由兩個參數作為條件。

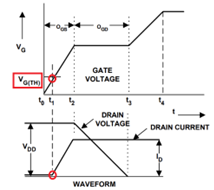

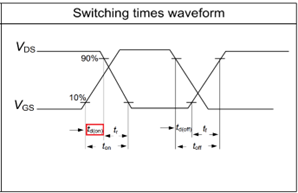

Vgs(th) & td(on).,請見圖二、圖三。

MOS 初導通的條件 : 電壓超過Vgs(th) 且持續時間大於td (on)

當電壓超過Vgs(th),id便會有微弱電流爬升。

而當經過td(on)時,Vds開始下降,則電流可視為完全流過MOS。

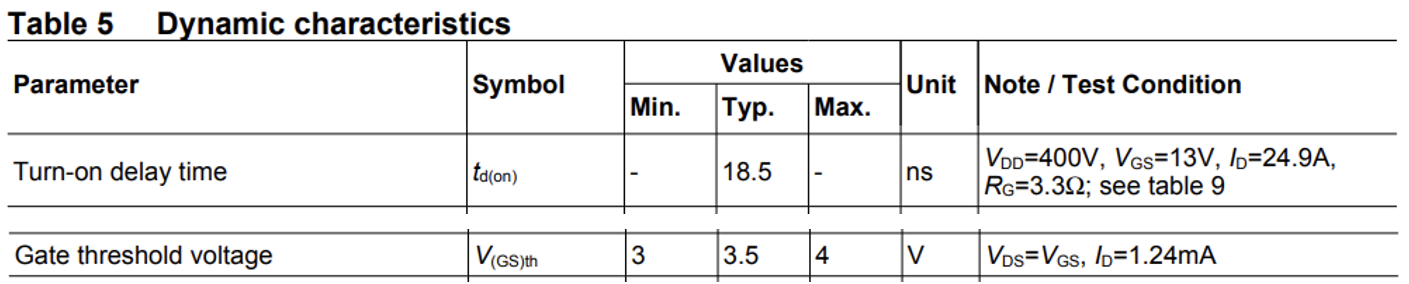

這兩個參數都於datasheet可以搜尋的到

Ex.以IPW60R040C7為例:

MOS Vgs完整充電行為:

而整個MOS 進入到完全導通狀態其實需要經過完整t1~t3區間。

當柵極連接到電源電壓時,VGS 開始增加,直到達到 Vth,此時漏極電流開始流動,CGS 開始充電。

在 t1 到 t2 期間,CGS 繼續充電,柵極電壓繼續上升,漏極電流按比例上升。在時間t2,CGS完全充電,漏極電流達到預定電流ID並保持恆定,同時漏極電壓開始下降。

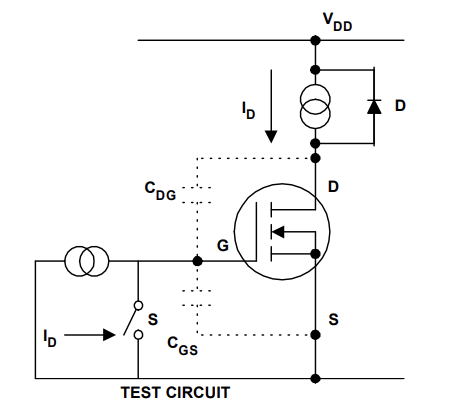

參考圖四所示的 MOSFET 等效電路模型,可以看出,當 CGS 在 t2 充滿電時,VGS 變為恆定,驅動電流開始對米勒電容 CDG 充電。這一直持續到時間 t3

由於 t2 和 t3 之間的快速變化的漏極電壓(電流 = C dv/dt),米勒電容的充電時間大於柵源電容 CGS 的充電時間。

一旦電容 CGS 和 CGD 都被完全充電,柵極電壓 (VGS) 再次開始增加,直到它在時間 t4 達到電源電壓。

對應於時間 t3 的柵極電荷 (QGS + QGD) 是開啟器件所需的最低電荷。

結論:

由上述可知,單論MOS導通有好幾種可能性

- 1:Vgs > Vgs(th) 的初導通

- 2:Vgs > Vgs(th) & t > td(on) 的MOS 導通

- 3:以及克服完整Miller平台後的MOS 全導通三者。

唯有Vgs突波波形條件比可能性2更大時,MOS才有誤開並且損傷的風險。

參考資料:

a) https://www.infineon.com/dgdl/mosfet.pdf?fileId=5546d462533600a4015357444e913f4f&redirId=117673

b) https://www.infineon.com/cms/en/product/power/mosfet/n-channel/500v-950v/ipw60r040c7/