1.功能說明

光電耦合元件是以光作為媒介來傳輸信號的一種元件,主要功能是讓輸入及輸出電路之間, 可以通過隔離的方式傳送電信號,光電耦合元件(英語:Optical coupler,或英語:Photo coupler),亦稱光耦合器、光隔離器以及光電隔離器,簡稱光耦。在兩個不共地的電路之間傳送 信號,即使兩電路之間有高壓也不會互相影響,提高其抗干擾能力和可靠度及穩定性,可用於開 關設備,或用在兩個需要隔離裝置之間的資料傳輸。

2.訊號特性

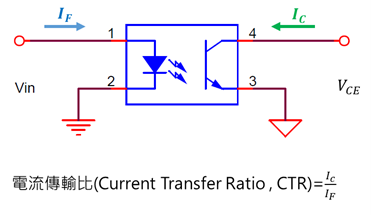

2.1 電流傳輸比(Current Transfer Ratio , CTR)

電流傳輸比(CTR)的定義為輸出電流和輸入電流的比值 (IC/IF)*100% 主要用來評估負載電阻值的選用,量測方式如圖 1 所示。

圖 1

2.2 訊號電壓準位

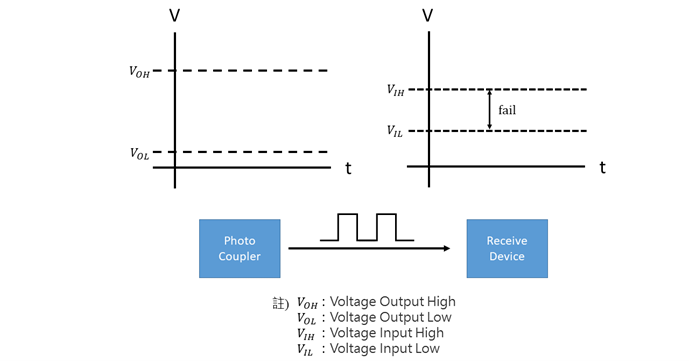

在數位邏輯中,可以用 0 或 1 來表示所有的訊號,VoH和VOL在提供接收端 1 和 0 的電壓值,VIH和VIL則在限制接收端判斷 1 和 0 的下限和上限電壓值,如圖 2 所示。

圖 2

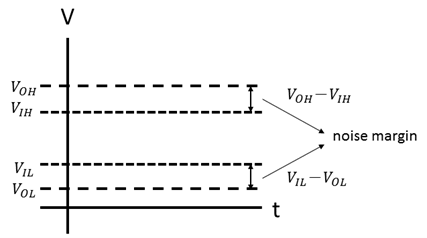

在邏輯電路中,常會因靜電或磁場的干擾,進而在接線上感應出電壓,此種不屬於原 電路的假訊號即為雜訊,而抵抗此雜訊的能力,可稱為雜訊容忍度(Noise margin),在此 範圍中的電壓訊號將視為雜訊。如圖3所示。

圖3

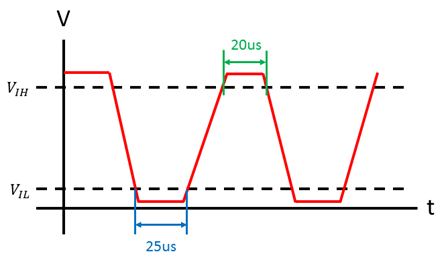

2.3 維持時間(Hold time):

除了訊號電壓值之外,通常還需要維持一段時間,才會被視為有效訊號,如圖 4 所示,假設高準位和低準位的維持時間(Hold time)需要大於 22us,才會被判斷為有效訊號,當 低準位為 25us,高準位為 20us,此時高準位則無法被當作有效訊號,可以用三種方式解決:

- l 延長輸入訊號高準位的時間,但需要降低輸入訊號的開關(傳輸)速度。

- l 降低負載電阻RL(Load resistance),但需要考量到是否能維持在飽和開關工作。

- l 可以調整訊號判斷的維持時間(Hold time),只局限使用軟體的方式來處理。

圖 4

3. LED 驅動電路

以下為三種常見的 LED 驅動方式: 3.1 GPIO(General-purpose input/output)控制

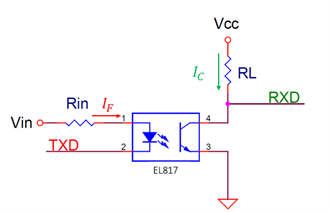

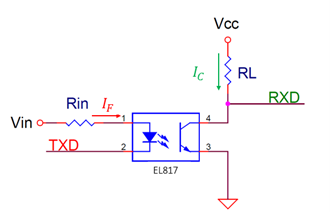

如圖 5 所示,輸入電源經由一電阻和 IR LED 串聯,改變電阻值可調整 IF 電流值,TXD 以 GPIO 控制。

圖 5

3.2 電晶體(BJT, bipolar junction transistor)驅動

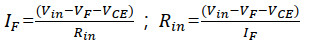

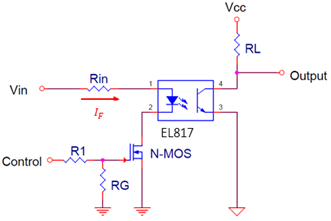

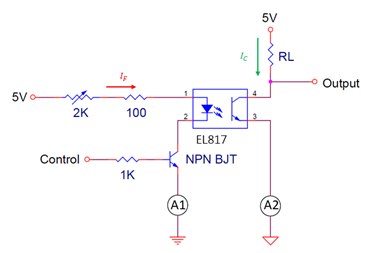

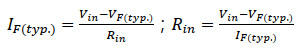

圖 6 使用 NPN 電晶體作為 LED 的開關使用,control 提供控制訊號, IF電流由Vin和Rin決定,Vin使用 DC 電源,輸入端可以使用較高的IF驅動電流,下列計算式用來評估IF和 Rin對應的數值。

圖 6

3.3 MOSFET(metal–oxide–semiconductor field-effect transistor)驅動:

圖 7 使用 N-MOSFET 作為 LED 的開關使用,control 提供控制訊號,輸入端可以使用較高的IF驅動電流,下列計算式用來評估IF和Rin對應的數值。

圖 7

4. 應用電路實測

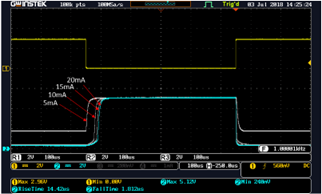

4.1 IF差異比較

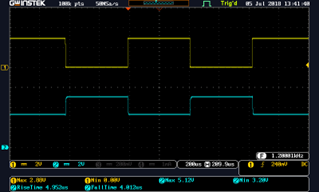

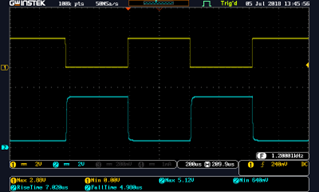

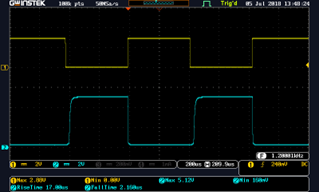

如圖 8 所示,使用 EL817 作為實測樣品,CTR%規格為 327% (@IF = 5mA),CH1 量測Control 訊號,CH2 量測 Output 訊號,調整不同IF電流,觀察 Output 輸出波形,如圖 9 所示,在 5mA 時,VOL尚有大於 1V 的電壓,假設後端接收裝置的VIL = 0.8V,低準位訊號便 是一個無效的輸出訊號,如圖 10~12,當IF = 10mA以上時,VOL已接近至 0V。如圖 13 所 示,比較輸入訊號關閉後,不同IF下 Output 電壓上升時的波形,可以發現較低的IF容易發 生低準位電壓過高的情況,這是因為輸出端光電晶體未在飽和開關下工作,而IF電流較大可 以讓IC更快達到上限電流。

圖 8

圖 9 IF= 5mA 圖 10 IF= 10mA

圖 11 IF = 15mA 圖 12 IF = 20mA

圖 13 IF of all

4.2 傳輸速度比較:

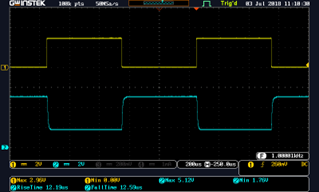

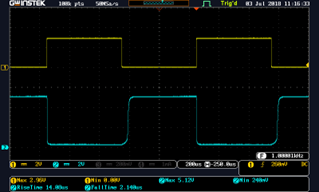

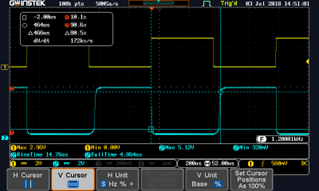

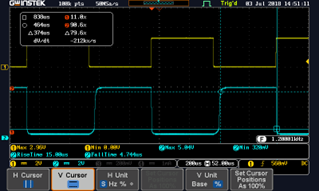

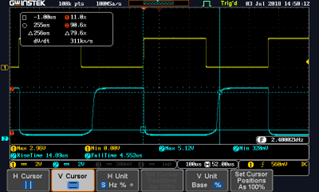

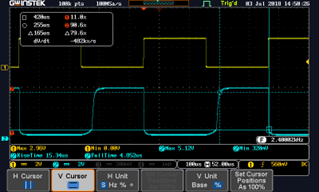

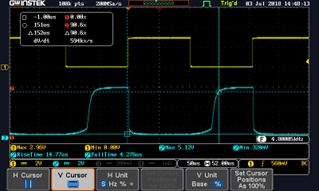

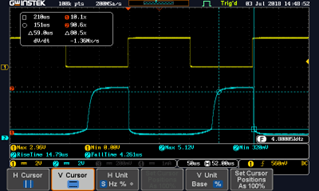

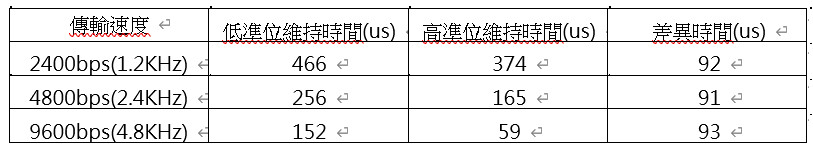

在IF= 10mA、RL = 1KΩ的條件下,測試 2400bps(1.2KHz)、4800bps(2.4KHz)、9600bps(4.8KHz)傳輸速度,比較高低準位的維持時間(Hold time)差異,如圖 14~19。

2400bps (1.2KHz):

圖 14 Low Level=466us 圖 15 High Level=374us

4800bps (2.4KHz):

圖 16 Low Level=256us 圖 17 High Level=165us

9600bps (4.8KHz):

圖 18 Low Level=152us 圖 19 High Level=59us

雖然高低準位的總時間是一樣的,但由於輸入端關閉後,輸出端恢復至高準位電壓的時 間比較長,造成維持時間(Hold time)變得更短,這在輸出端裝置判斷高準位時,可能被認為 是無效訊號。如表格 1 所示,兩者之間的差異雖然不會因為頻率的改變而有所變動,但是頻 率越快時,高準位佔空比(duty)越來越短。

表格 1

4.3 RL差異比較:

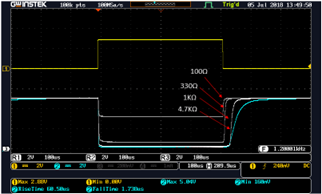

如圖 20 所示,當RL=100Ω,因 CTR%=327% ,可得IC = 16.35mA、 VRL = 16.35mA ∗100 = 1.635V、VCE = 5 − 1.635 = 3.265V。VCE電壓低準位約 3.265V 左右,加大RL使得VCE進入飽和開關工作,如圖 21 所示,將RL增加至 330Ω後,VCE已逐漸下降,如圖 22 所示, 接著再將RL增加至 1KΩ,此時VCE已接近 0V,如圖 23 所示,再將RL加大至 4.7K,則VCE回 復至高準位電壓則需要更長的時間,如圖 24 所示,RL=1KΩ不僅工作在飽和開關,也有著較快的轉態時間。

圖 20 RL=100Ω 圖 21 RL=330Ω

圖 22 RL=1KΩ 圖 23 RL=4.7KΩ

圖 24 RLof all

5.如何有效的設計電路

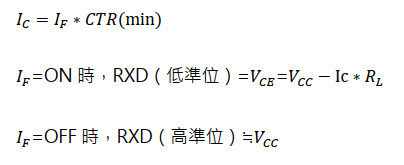

在設計電路時,首先需要知道??輸入電流、CTR 的範圍、負載電阻RL數值三者之間的關係,則可預先評估輸出訊號的高、低電壓準位,圖 25 為 UART 傳輸的參考電路。

圖 25

當 TXD=0時,

因為較低的 CTR 比較不容易達到飽和開關的狀態,所以會取 CTR 的最小值來計算(需考慮到 IF電流和環境溫度TA的影響)。

評論