偏置電阻內置晶體管 (BRT),也稱為數字晶體管,設計用作開關。 BRT 是一種包含串聯基極電阻器 (R1) 和基極-發射極電阻器 (R2) 的雙極晶體管,可以簡化板上電路設計。東芝半導體有一系列的BRT的產品可以選擇

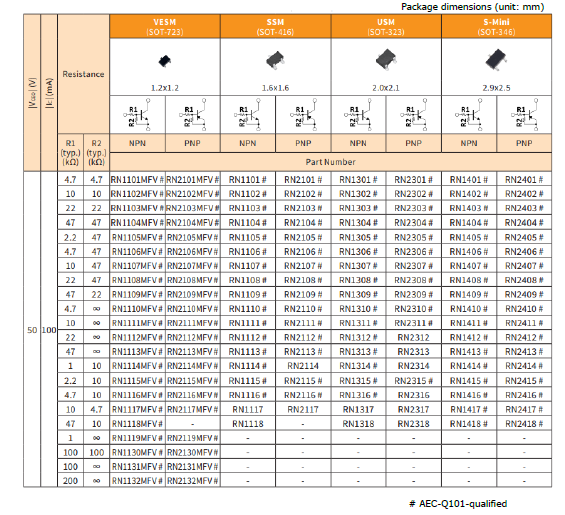

以下為BRT的Lineup

關於BRT的選用

可以參考以下的選用來當成依據

以下圖一說明

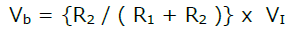

當施加到B端子的控制電壓(VI)從截止狀態增加時,結合了NPN雙極晶體管的BRT在飽和區域中如何導通。為了簡單起見,讓我們考慮圖1所示的簡單電路的操作

- 雙極晶體管Q截止。

VI 逐漸增加。由於Q最初是關斷的,因此VI產生的電流僅流向R1和R2。因此,VI被R1和R2劃分,並且Vb施加於Q的基極(b)。

圖.1用於說明BRT工作的電路

- Q從關閉變為打開。

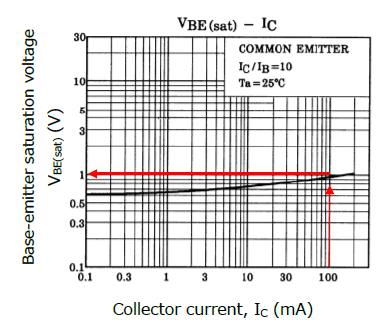

當Vb達到約0.6 V時,基本電流(Ib)開始流動,導通Q,如圖2 所示的VBE(sat)-IC曲線所示。這將導致Ib乘以hFE的集電極電流流動。在此時間點,Q仍在有源區域中,而不在飽和區域中。因此,與通用雙極型晶體管(例如2SC2712)的hFE一樣,其hFE為120至700。

- Q打開。 (從有效區域到飽和區域的過渡)

隨著VI進一步增加,VBE也增加。當內部雙極晶體管的基極電壓(Vb)高於0.6 V時,Vb的輕微升高會導致集電極電流(IC)呈指數增長,如圖2-2的VBE(sat)-IC曲線所示。

因此,一旦Q導通,Vb幾乎保持不變,而不受VI除以R1和R2的影響。流過R1的所有多餘電流(IB-IR2)作為基極電流(Ib)流到雙極晶體管。當雙極晶體管導通時,它仍處於集電極電流(IC)為IB * hFE的有源區域。但是,由於集電極-發射極電壓(VCE)等於VCC – RL * IC,由於IC的增加,VCE突然降低,導致雙極晶體管進入飽和區。

在該區域中,基極-發射極和基極-集電極的pn結均被正向偏置。因此,大量的少數載流子累積在基極區域中。

- Q從打開變為關閉。

VI上的電壓降低。但是,將VI降低到指定為“輸入電壓(OFF)”的電壓以下不會導致雙極晶體管立即關閉。這是因為集電極電流持續流動,直到基極區域中的所有少數載流子都通過R2放電或由於與多數載流子復合而消失。此操作所需的時間稱為存儲時間tstg。少數子載波消失後,Q關閉。

圖2 VBE(sat)-Ic曲線(2SC2712) 圖3 BRT的工作位置

電氣特性作為開關

BRT開啟時,開關端子兩端的電壓(VCE(sat))

VCE(sat)是集電極-發射極電壓(VCE)。

a)機械開關 b)BRT開關

圖4: 開關端子之間的電壓

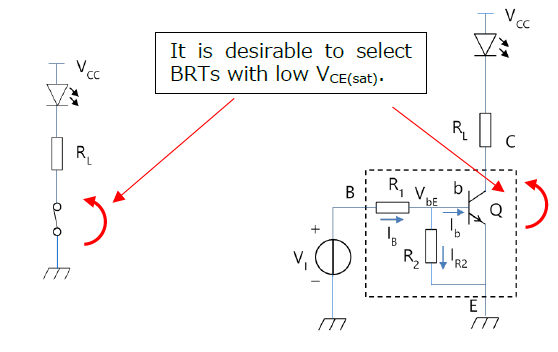

機械開關閉合時,端子之間的電阻幾乎為零。但是,對於BRT,必須在集電極-發射極電阻低(即,集電極-發射極電壓低)的飽和區域中使用它。在有源區域,集電極電流根據hFE與基極電流成比例增加。相反,在飽和區域中,hFE隨著飽和度的增加而降低(即,VCE降低)。圖5 顯示了BRT的IC–VCE曲線,其中VCC為5 V時的負載線以紅色突出顯示。負載線在VCE為3.8 V時與IB = 0.2 mA曲線相交,這意味著當IB = 0.2 mA時hFE = 160。但是,負載線在VCE為0.2 V時與IB = 6 mA曲線相交,意味著hFE = 20。因此,有兩種降低集電極-發射極電壓(VCE)的

方法:

- 降低集電極電流(增加負載電阻RL)。

(紅色負載線⇒藍色負載線)

- 增加基極電流Ib。

圖5: 降低VCE的飽和電壓

由於通過增加RL來降低VCE(sat)的第一種方法會影響負載電流(IC),因此只能將集電極電流減小到設計要求所允許的程度。在這裡,讓我們看看增加基極電流如何幫助降低VCE(sat)。

查看圖3-1(b)所示的電路。假設我們正在將RN1102 BRT(R1 = R2 = 10kΩ)的控制電壓(VI)從0 V更改為5 V.

如果沒有雙極晶體管,將VI從0 V增加到5 V顯然會導致b(Vb)處的電壓從0 V變為2.5 V,這是因為R1和R2值之比。然而,實際上,由於存在雙極晶體管,VbE僅增加到大約1 V,如圖3-3所示。剩餘電流以Ib的形式流向基極端子:

如該方程式所示,可以通過使用BRT通過增加IB並降低IR2來增加Ib:

減1小R1值

加大R2值

這裡重要的是R1和R2的絕對值,而不是R1與R2的比率。

集電極-發射極的飽和電壓隨著溫度的升高而增加,如圖6所示。考慮上述特性以實現最佳設計。

圖6: VBE(sat) – Ic曲線(2SC2712)

圖7:VCE(sat)- Ic Ic曲線(RN1102)

如需瞭解有關TOSHIBA BRT更多資訊,請按一下以下連結