在數字電路的設計中觸發器是必不可少的,因為觸發器是一種具有記憶功能,可以存儲二進制信息的雙穩態電路,是組成時序邏輯電路的基本單元,比如RS觸發器,D觸發器,JK觸發器等等,這裡著重介紹以上所提兩種觸發器即RS觸發器和D觸發器。

1. RS觸發器

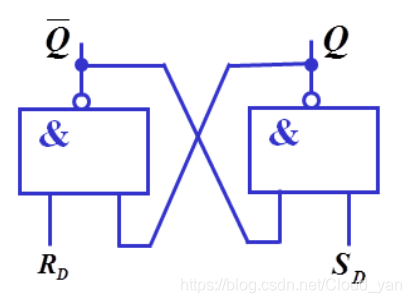

RS觸發器是構成其他觸發的根本,其構成可以用兩個與非門或者兩個或非門交錯耦合構成,其邏輯電路如下圖1所示:

圖1 RS觸發器邏輯電路圖

由邏輯電路圖可知,當R=0,S=0時,輸出的Q時不確定的,當R=1,S=1時,會保持原本的狀態不變,因此可得到如下真值表:

|

R |

S |

Qn |

|

0 |

0 |

不確定 |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

Qn-1 |

由以上真值表可得知RS觸發器具有置0功能,置1功能以及存儲功能。

2. D觸發器

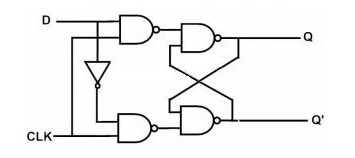

『D觸發器也稱為“延遲觸發器”或“數據觸發器”,主要作為是用於存儲1位二進制數據,D觸發器是有兩個輸入,一個時鐘信號(CLK)輸入和一個數據(D)輸入,此外,D觸發器也有兩個輸出,一個是Q表示主輸出,一個是Q‘表示Q的補碼,D觸發器是通過修改RS觸發器來進行構造的。』(注1)其中,S輸入由D輸入給出,R輸入由反向D輸入給出。因此,D觸發器類似於RS觸發器,其中兩個輸入相互補充,所以不會出現任何中間狀態。D觸發器的電路圖如下圖2所示:

圖2 D觸發器的電路圖

D觸發器工作原理是當不向D觸發器試駕任何時鐘輸入或者時鐘信號的falling edge期間,輸出不會發生變化即保持原本的輸出的值,如果時鐘信號位rising edge,那麼輸出的數字信號將由輸入信號決定。其真值表如下:

|

CLK |

D |

Q |

Q’ |

|

FALLING EDGE |

X |

Q |

Q’ |

|

RISING EDGE |

1 |

1 |

0 |

|

RISING EDGE |

0 |

0 |

1 |

時序圖3如下所示:

圖3 D觸發器時序圖

總結

在各種各樣的數字電路或者數字IC(比如NOVATEK的NT37xxx系列)的中,因為數字電路對於時序信號要求的嚴格性,因此觸發器是必不可少的。

Q&A

Q:D觸發器一般可以用做什麼呢?

A:D觸發器一般可以作為數據存儲寄存器,同時也可以作為移位寄存器的數據傳輸,以及分頻電路。

Q:RS觸發器的存儲功能能舉個具體例子嗎?

A:當斷電前“S=0,R=1”,此時Q=0,Q’=1。斷電後,“S=0,R=0”,此時Q’=1,R=0,輸出的Q依舊是0;Q=0,S=0,輸出的Q’依舊是1.這就做到了保持Q不變,實現了存儲功能。

Q:能具體說一說觸發器有哪些嗎?

A:基本的觸發器是RS觸發器,JK觸發器,T觸發器,D觸發器,其他的觸發器基本是通過這些觸發器變形而來.

Q:與非門是什麼?

A:與非門即對輸入的數據先與在取非,比如輸入的數據D1=1,D2=1,那麼D1&D2=1,再對此值取非,即最終值為0。

Q:CLK的falling edge與rising edge分別是什麼?

A:標準的CLK信號一般是由周期性變化的方波組成,在一個周期內,方波的構成中是有上升部分以及下降部分,如下圖4所示:

圖4 方波

注1:作者:IC先生網;出處:https://www.elecfans.com/d/1903284.html

評論