一、前言

本文以世平集團推出的 NXP Echoes-S32K144 評估板為例,使用配置 I2C 模塊發送與接收數據,為了更直觀觀察 LPI2C 的工作效果,我們發送命令控制 Buck_boost CPSQ5206 並每秒發送讀取命令讀取 CPSQ5206 內部寄存器狀態使用 LPUART 列印。

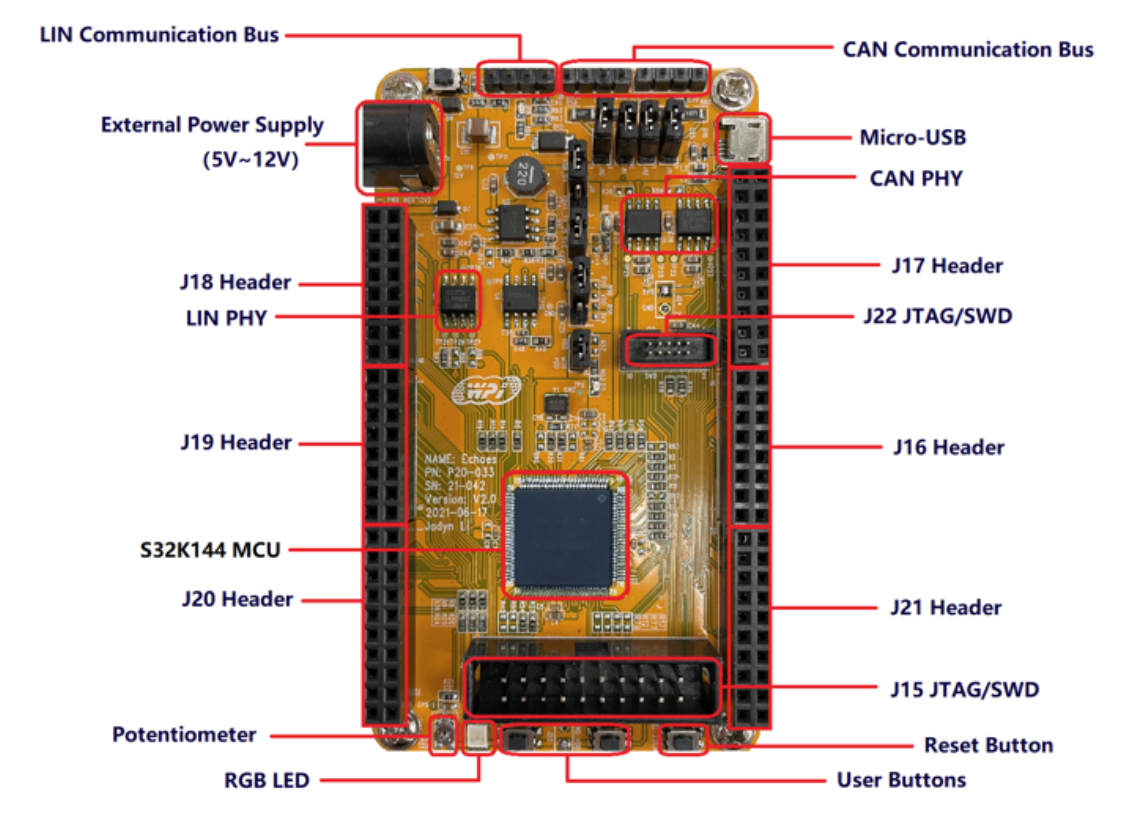

S32K144 是恩智浦(NXP)公司於 2017 推出面向通用汽車應用市場的高性能微處理器,該微處理器基於 32位 ARM Cortex-M4F 內核,最快內核頻率達 112MHz。NXP Echoes-S32K144評估板採用 14×14mm LQFP100 封裝,引腳間距 0.5mm,具有豐富的外設資源。該方案支持 JTAG 標準調試接口和 JTAG 4 線 SWD 調試模式,具有 micro USB 或外部 12V 電源兩種供電選擇,板載 CAN、LIN 與 UART 連接。

圖 1-1 NXP Echoes-S32K144評估板

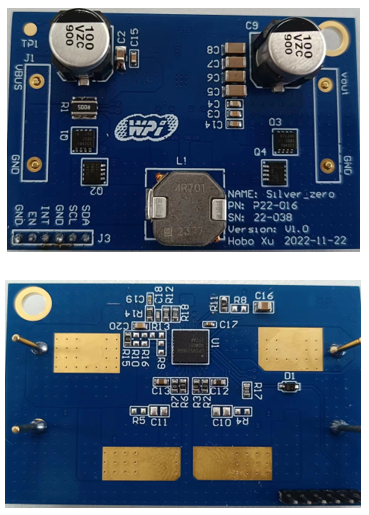

Silver_zero 是大聯大世平集團推出的一款 DC/DC 電壓調節方案,採用數字控制式 Buck_Boost CPSQ5206C。CPSQ5206 是AEC-Q100 認證的同步 4 開關 Buck-Boost 控制器,支持 3.8V 到 36V 的寬輸入電壓範圍,並提供解析度為10mV 的 2.0V 到 36V 可編程輸出電壓。當使用 5mΩ 電流傳感電阻時,控制器可輸出解析度為 50mA 高達 8A 的調節電流。為確保變流器的安全運行 CPSQ5206 還提供輸入/輸出過壓保護、輸出短路保護、MOSFET 逐周期限流和熱關機等全面保護。

圖 1-2 Silver_zero

本文將各模塊獨立介紹並在各模塊章節中講解初始化函數代碼,最後在主函數代碼章節中調用各模塊初始化函數。由於模塊頭文件為各函數聲明,所以本文默認各頭文件聲明已創建並編寫無誤,若未有頭文件,可創建 .h 文件並將各函數名複製到 .h 文件中編譯成功即可。

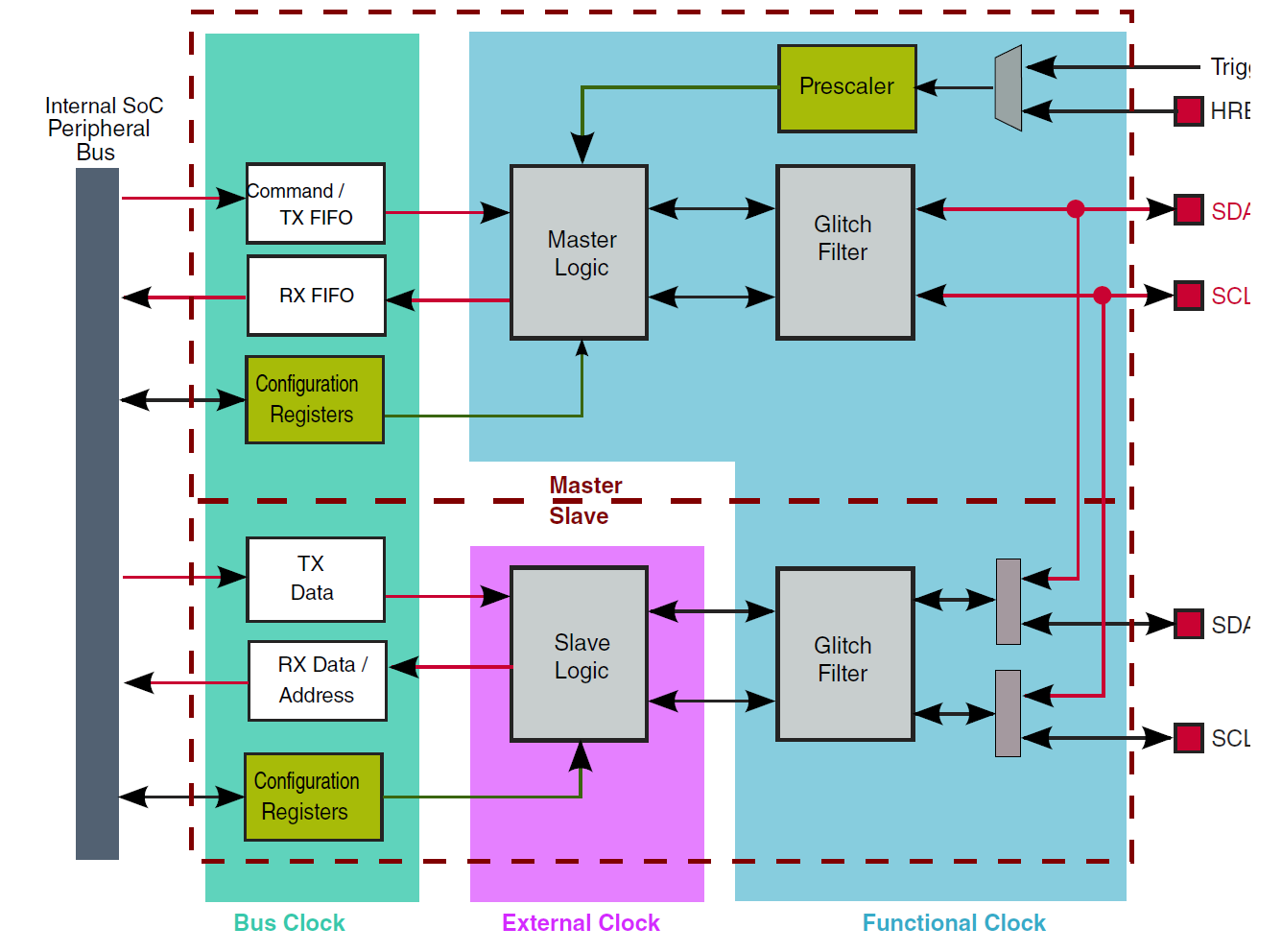

二、S32K144 I2C 模塊

2.1 S32K144 I2C 模塊介紹

LPI2C 是一種低功耗的集成電路間(I2C)模塊,它可以作為主設備或者從設備的 I2C 總線的有效接口。如果存在可用的適當時鐘,該模塊可以在停止模式下繼續運行,並且設計用於低 CPU 減輕 DMA 訪問 FIFO 寄存器消耗。

LPI2C 模塊同樣符合系統管理總線(SMBus) 2.0 規範。

S32K144 具有 1 個 LPI2C 模塊,這些模塊具有以下特點:

LPI2C 支持以下 I2C 規範功能:

- 支持標準、快速、快速+和超快模式。

- 從機支持 HS 模式。

- 如果 SCL 引腳實現電流源上拉(設備特定),主機將支持 HS 模式。

- 支持多主機,包括同步與仲裁。

- 時鐘展寬。

- 通用調用,7 位和 10 位尋址。

- 軟體復位、START 字節和設備 ID 需要軟體支持。

LPI2C 主機支持以下功能:

- 命令/發送 4 字 FIFO。

- 命令 FIFO 將在啟動傳輸之前等待空閒 I2C 總線。

- 命令 FIFO 可以啟動(重複)START 和 STOP 條件以及一個或多個主接收機傳輸。

- STOP 條件可以從命令 FIFO 生成,或在傳輸 FIFO 為空時自動生成。

- 主機請求輸入可以用於控制 I2C 總線發送的開始時間。

- 靈活的接收數據匹配可以在數據匹配時產生中斷或者丟棄不需要的數據。

- 標誌和可選中斷,用以發送重複啟動條件、停止條件、仲裁丟失、意外 NACK 和命令字錯誤的信號。

LPI2C 從機支持以下功能:

- 單獨的 I2C 從機寄存器,可以做大限度地減少由主從機切換造成的軟體消耗。

- 支持 7 位或 10 位尋址、地址範圍、SMBus 警報和通用呼叫地址。

- 發送數據寄存器支持中斷或 DMA 請求。

- 接收數據寄存器支持中斷或 DMA 請求。

- 軟體可控制的 ACK 或 NACK,具有 ACK/NACK 位上的可選時鐘擴展。

- 可配置時鐘展寬,以避免傳輸 FIFO 不足和接收 FIFO 超時。

- 標誌和可選的數據包結束中斷、STOP 條件或位錯誤檢測。

圖2.1-1 LPI2C 框圖

2.2 S32K144 LPI2C 工作模式與信號描述

表2.2.1 LPI2C 模塊支持的晶片模式

|

晶片模式 |

LPI2C 工作 |

|

運行模式 |

正常工作 |

|

停止或等待模式 |

如果 Doze Enable 位(MCR[DOZEN])置 0,且 LPI2C 使用外部或內部時鐘源在停止或等待模式下保持運行,則 LPI2C 可以繼續運行 |

|

低泄漏停止模式 |

Doze Enable(MCR[DOZEN])位被忽略,LPI2C 將在確認進入低泄漏模式之前等待電流傳輸完成任何未決操作。 |

|

調試模式 |

如果調試使能位(MCR[DBGE])置位,LPI2C 將會繼續運行。 |

表2.2.2 LPI2C 模塊信號描述

|

信號 |

描述 |

I/O |

|

SCL |

LPI2C 時鐘線。在四線模式下是 SCL 輸入引腳。 |

I/O |

|

SDA |

LPI2C 數據線。在四線模式下是 SDA 輸入引腳。 |

I/O |

|

HREQ |

如果 I2C 總線空閒並且被置位的情況下,主機請求可以發起 LPI2C 主傳輸。 |

I |

|

SCLS |

I2C 輔助時鐘線。在四線模式下是 SCLS 輸出引腳。如果 LPI2C 主/從被配置成單獨使用的引腳,則是 LPI2C 的從 SCL 引腳。 |

I/O |

|

SDAS |

I2C 輔助數據線。在四線模式下是 SDAS 輸出引腳。如果 LPI2C 主/從被配置成單獨使用的引腳。則是 LPI2C 的從 SDA 引腳。 |

I/O |

2.3 S32K144 LPI2C 寄存器介紹

LPI2C 模塊由 28 個 32 位寄存器構成,這些寄存器又分為主機寄存器與從機寄存器,詳細的寄存器映射見下表。

表2.3.1 LPI2C Memory Map

|

Offset |

Register |

Width (In bits) |

Access |

Reset value |

|

0h |

Version ID Register (VERID) |

32 |

RO |

01000003h |

|

4h |

Parameter Register (PARAM) |

32 |

RO |

00000202h |

|

10h |

Master Control Register (MCR) |

32 |

RW |

00000000h |

|

14h |

Master Status Register (MSR) |

32 |

W1C |

00000001h |

|

18h |

Master Interrupt Enable Register (MIER) |

32 |

RW |

00000000h |

|

1Ch |

Master DMA Enable Register (MDER) |

32 |

RW |

00000000h |

|

20h |

Master Configuration Register 0 (MCFGR0) |

32 |

RW |

00000000h |

|

24h |

Master Configuration Register 1 (MCFGR1) |

32 |

RW |

00000000h |

|

28h |

Master Configuration Register 2 (MCFGR2) |

32 |

RW |

00000000h |

|

2Ch |

Master Configuration Register 3 (MCFGR3) |

32 |

RW |

00000000h |

|

40h |

Master Data Match Register (MDMR) |

32 |

RW |

00000000h |

|

48h |

Master Clock Configuration Register 0 (MCCR0) |

32 |

RW |

00000000h |

|

50h |

Master Clock Configuration Register 1 (MCCR1) |

32 |

RW |

00000000h |

|

58h |

Master FIFO Control Register (MFCR) |

32 |

RW |

00000000h |

|

5Ch |

Master FIFO Status Register (MFSR) |

32 |

RO |

00000000h |

|

60h |

Master Transmit Data Register (MTDR) |

32 |

WORZ |

00000000h |

|

70h |

Master Receive Data Register (MRDR) |

32 |

RO |

00004000h |

|

110h |

Slave Control Register (SCR) |

32 |

RW |

00000000h |

|

114h |

Slave Status Register (SSR) |

32 |

W1C |

00000000h |

|

118h |

Slave Interrupt Enable Register (SIER) |

32 |

RW |

00000000h |

|

11Ch |

Slave DMA Enable Register (SDER) |

32 |

RW |

00000000h |

|

124h |

Slave Configuration Register 1 (SCFGR1) |

32 |

RW |

00000000h |

|

128h |

Slave Configuration Register 2 (SCFGR2) |

32 |

RW |

00000000h |

|

140h |

Slave Address Match Register (SAMR) |

32 |

RW |

00000000h |

|

150h |

Slave Address Status Register (SASR) |

32 |

RO |

00004000h |

|

154h |

Slave Transmit ACK Register (STAR) |

32 |

RW |

00000000h |

|

160h |

Slave Transmit Data Register (STDR) |

32 |

WORZ |

00000000h |

|

170h |

Slave Receive Data Register (SRDR) |

32 |

RO |

00004000h |

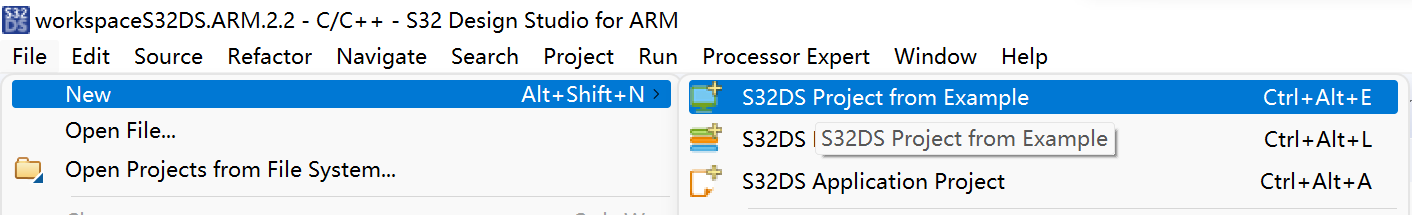

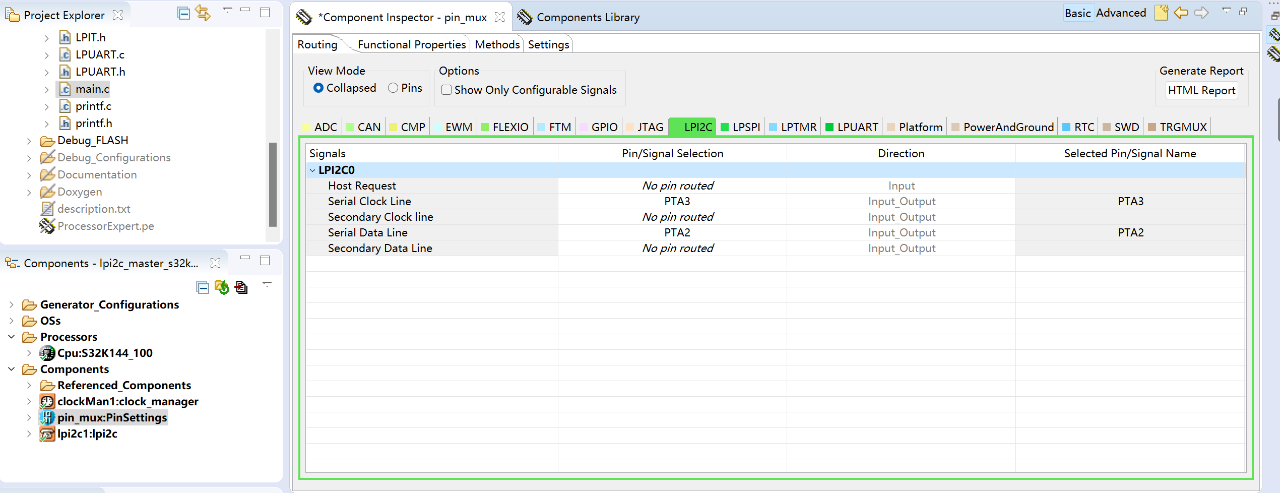

2.4 S32K144 LPI2C 例程導入

由於 LPI2C 寄存器過多直接對寄存器編程操作過於繁雜,所以我們使用 S32DS 內的庫函數進行編程具體操作如下。(IDE:S32 Design Studio for ARM Version 2.2;SDK:S32K1xx RTM v3.0.0)

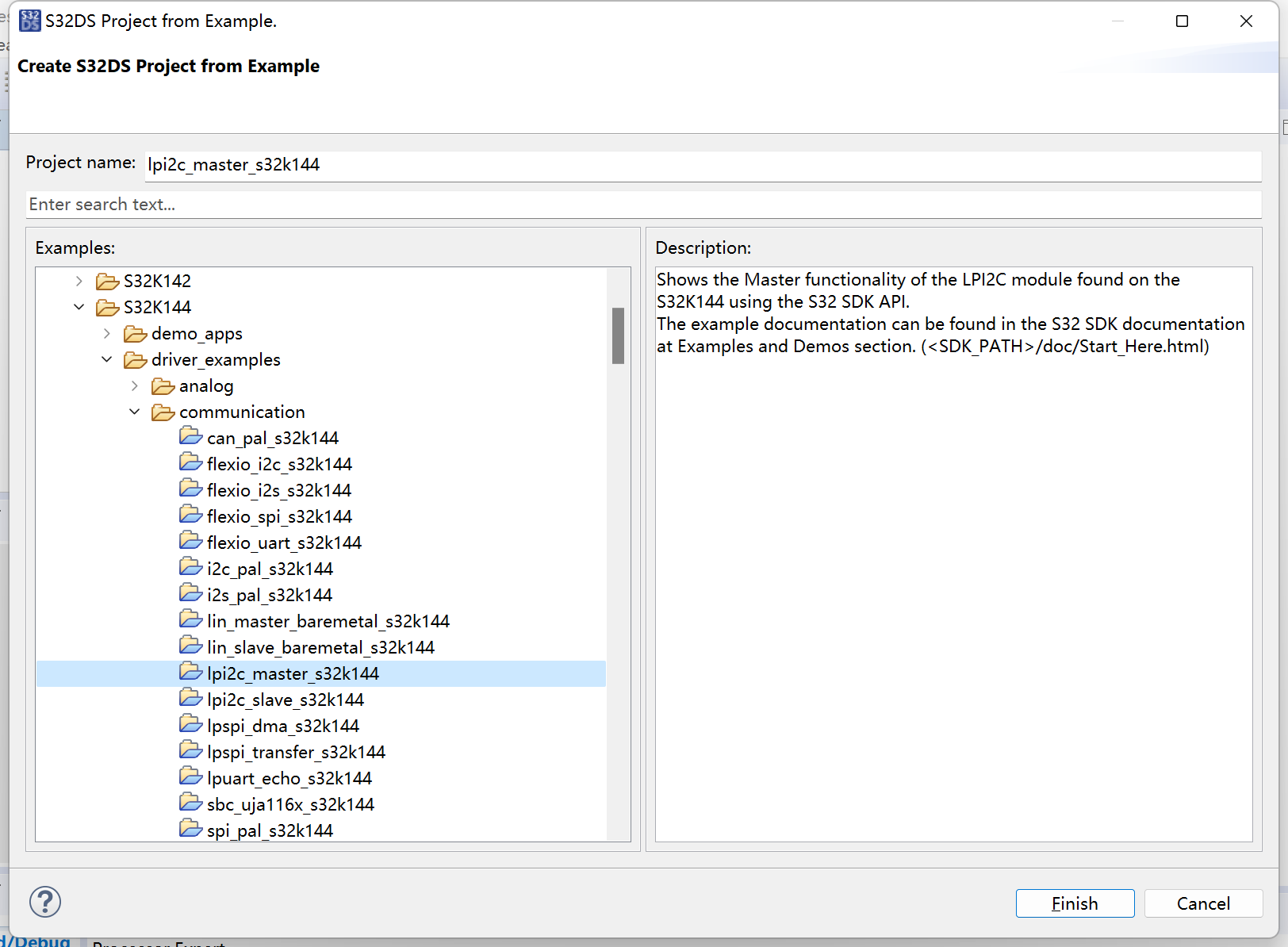

- 打開S32 Design Studio,點擊:“File”->“New”->“S32DS Project from Example”。

- 在彈出的窗口選取 S32K144 目錄下的 lpi2c_master 例程,點擊“Finish”。

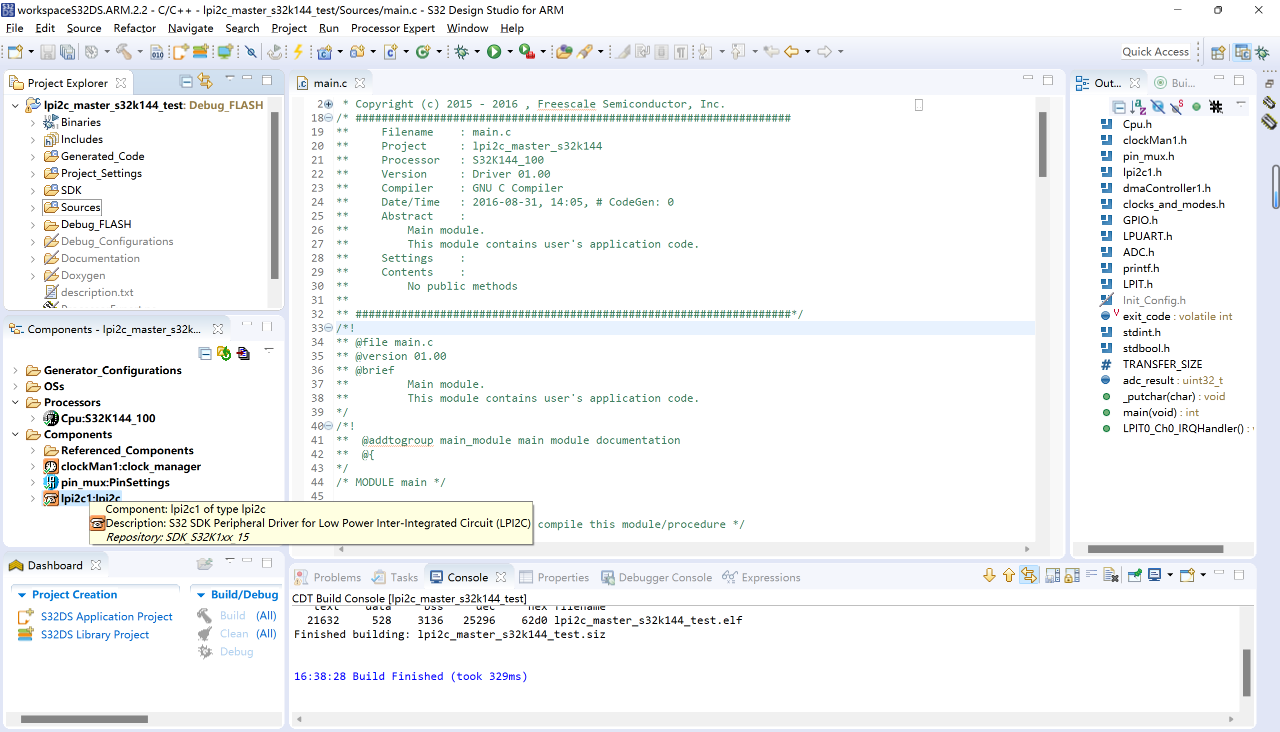

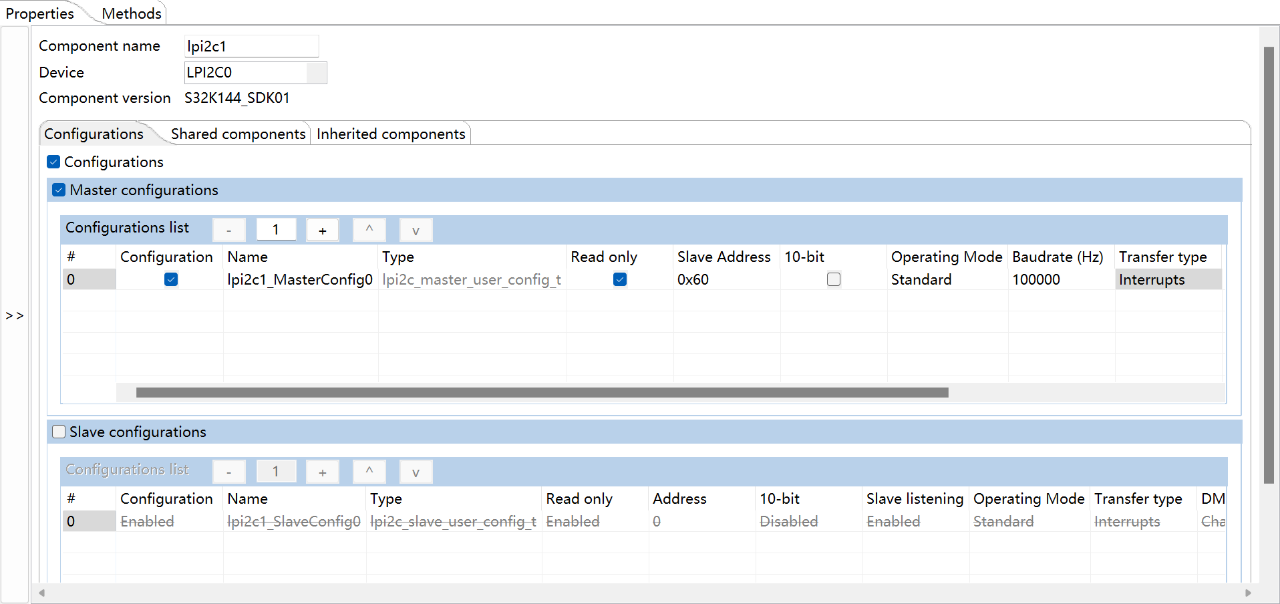

- 導入例程後雙擊左側的“lpi2c1:lpi2c”按鈕進入 I2C 配置。

- 在跳出窗口內將 Slave Address 設置成 0x60,Operating Mode 設置成 Standard,Baudrate (Hz) 設置成 100000。(CPSQ5206 晶片 I2C 地址可選地址為 60H、62H,由外部電路決定,Silver_zero 的外部電路設計確定其 I2C 地址為 60H。)

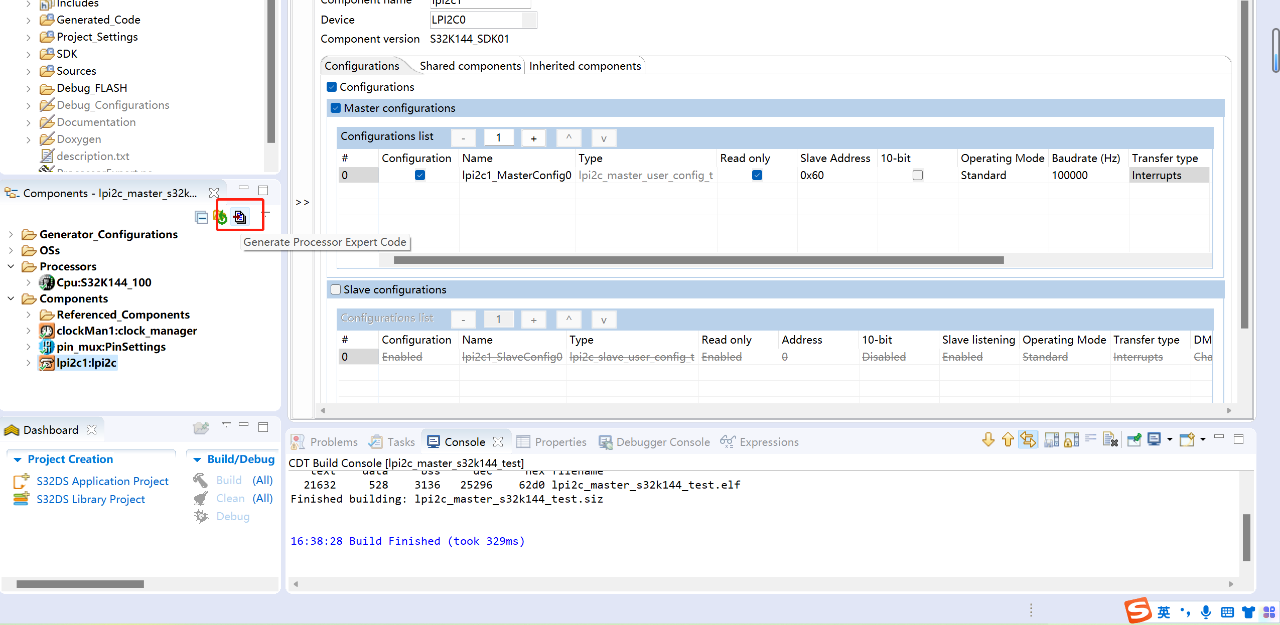

- 設置完成後點擊左側紅框內生成代碼按鈕進行代碼更新。

- 在引腳復用配置中將 PTA3 配置成 SCL,PTA2 配置成 SDA 隨後點更新代碼按鈕。

- 點擊左上角“Build”按鈕,編譯程序。

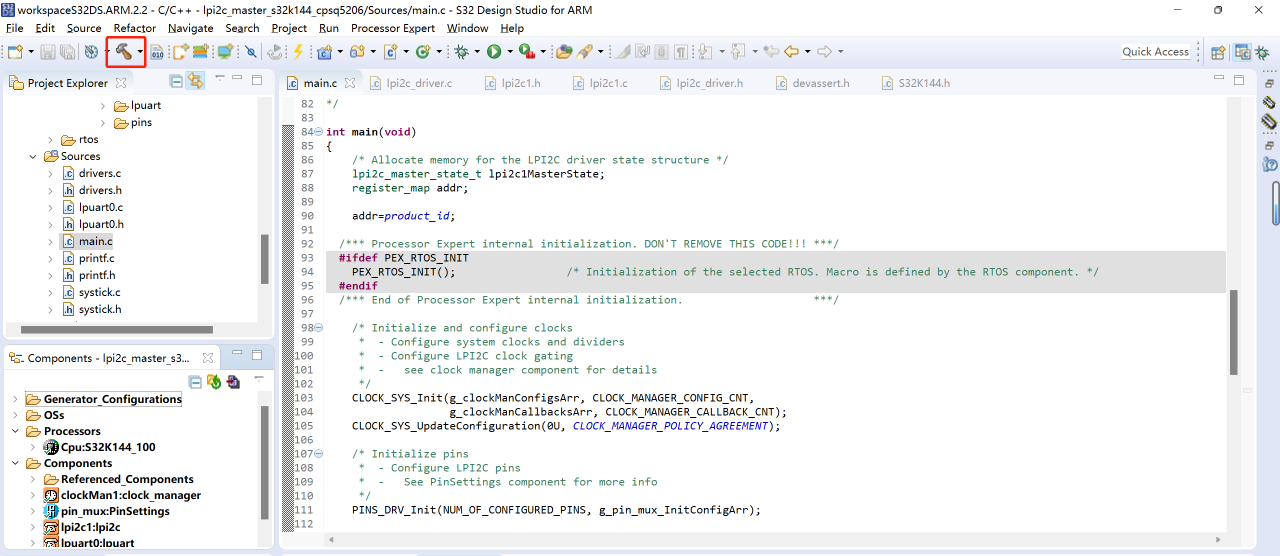

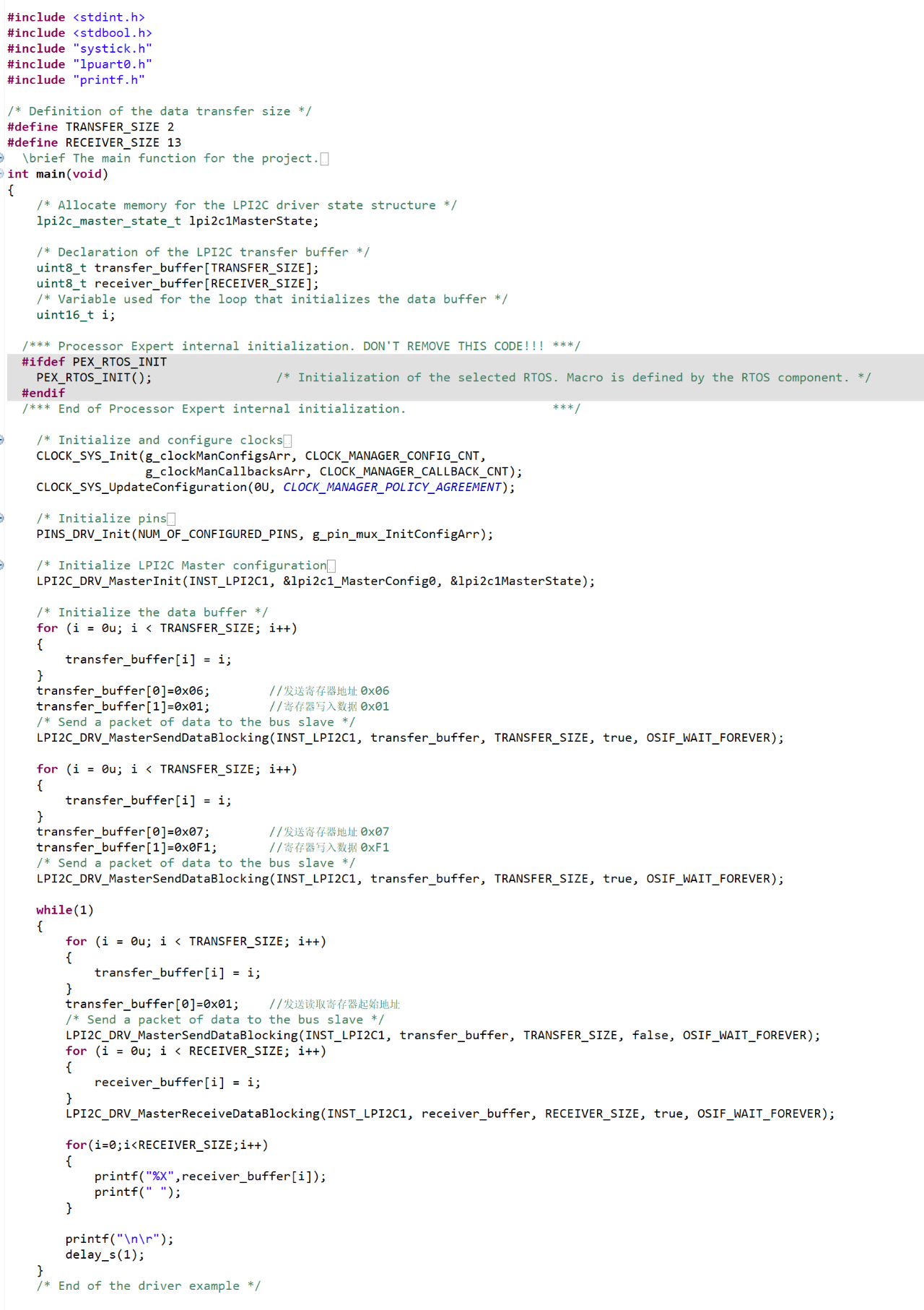

三、代碼編寫與測試

3.1 代碼編寫

為了更直觀觀察 LPI2C 模塊的讀取結果,還調用了 Systick 與 LPUART 模塊來每隔 1 秒通過 LPUART 發送一次 LPI2C 模塊的讀取結果,Systick、LPUART 模塊初始化與 Printf 函數代碼編寫較長本文不在此贅述。

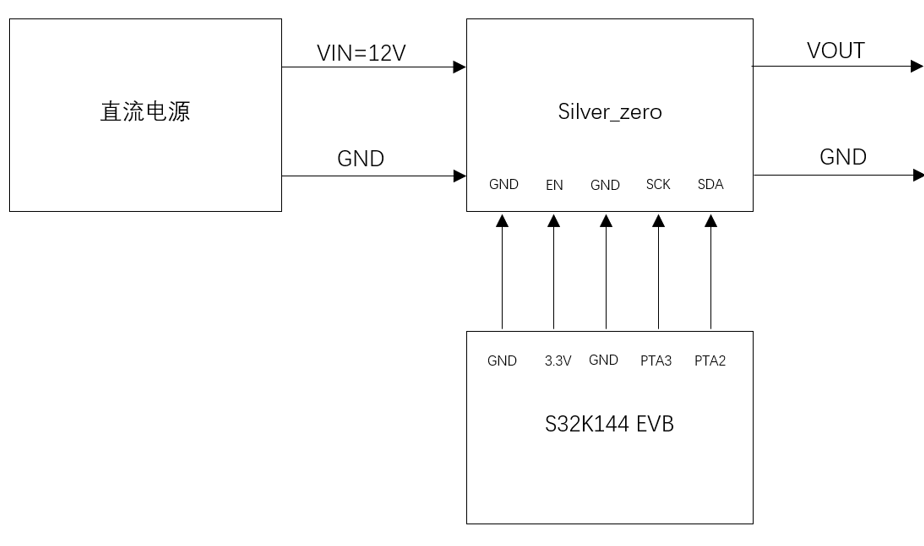

3.2 調試測試

按圖將直流電源、Silver_zero 與S32K144 EVB連接。直流電源與 Silver_zero J1 的 VBUS 和 GND 連接為 Silver_zero 提供 12V 直流電,S32K144 EVB 與 Silver_zero J3 連接,各引腳的對應關係如下,Silver_zero 的J2 為 VOUT、GND。使用示波器測量 VIN、SW1(電感左側)、SW2(電感右側)與 VOUT 並記錄波形,同時記錄串口發送 CPSQ5206 當前工作狀態。

設備連接圖

S32K144 EVB 與 Sliver_zero 引腳對應表

|

Silver_zero |

SDA |

SCL |

GND |

INT |

EN |

GND |

|

S32K144 EVB |

PTA2 |

PTA3 |

GND |

|

3.3V |

GND |

註:INT 引腳 CPSQ5206 分壓反饋引腳,使用外部分壓反饋時連接,Silver_zero 使用內部分壓反饋無需連接。

VIN=12V,L=4.7uH, FSW=400KHZ,CH1:VIN,CH2:OUT,CH3:SW1,CH4:SW2。

串口成功列印 log 與 CPSQ5206 數據手冊默認工作狀態和寫入數據相同,代碼成功運行。

四、參考文獻

[1] S32K144 Reference Manual.pdf,NXP

[2] S32K1xx Series Cookbook.pdf,NXP

[3] S32K144_IO_Signal_Description_Input_Multiplexing,NXP

[4] PCB - P20-033 Echoes_V2.0_Jadyn Li_20210618, 大大購

[5] CP-D-31-CA01-Rev0.2 CPSQ5206_Datasheet, CPS

歡迎在博文下方留言評論,我們會及時回復您的問題。如有更多需求,歡迎聯繫大聯大世平集團 ATU 部門:atu.sh@wpi-group.com

作者:Hobo Xu / 許寧

評論