前言:

對於目前電子產品而言,無不追求高效能及輕薄短小。而高效能與輕薄短小,這兩者卻是相違背的。

為了因應目前消費產品的潮流趨勢,各零件廠商對於這類的整合式電源產品,都紛紛投入研發資源,以期望能開發更小的封裝尺寸,更大的乘載電流。

以AOS 產品來看,目前開發出6A ~ 40A 左右的POL,其封裝尺寸僅為QFN 2x3 ~ QFN 5x6。這樣的零件的尺寸對於目前有限的PCB 板材空間而言,確實對於產品設計有著莫大的幫助。再者,乘載電流大及較高的轉換效率,也對於高效能產品的要求,也提供了一個更佳的選擇。

以下針對AOS POL的產品,有幾個能讓設計應用更為穩定的想法,就讓我們來討論一下。

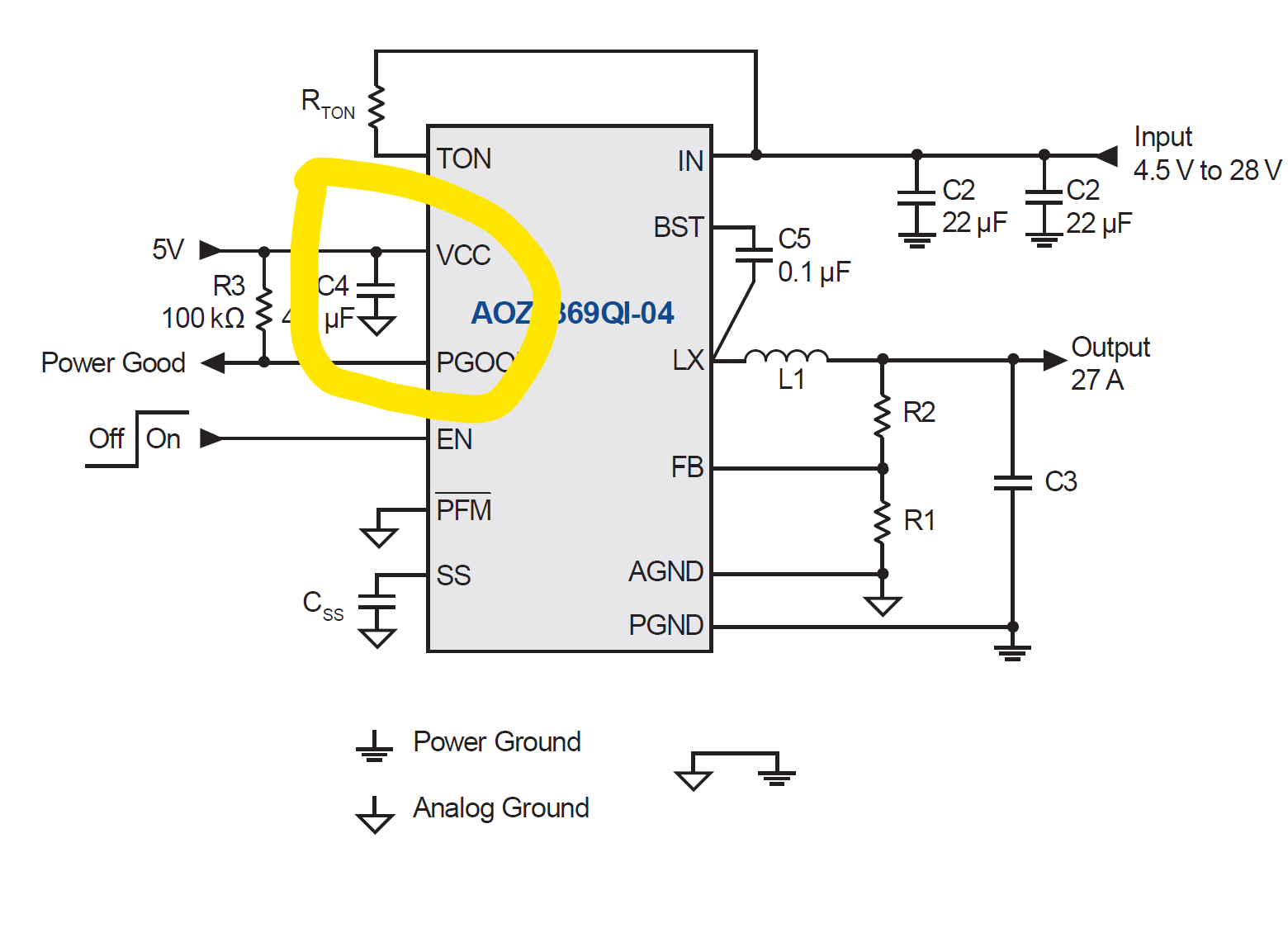

- POL VCC穩壓電容的處理:

其POL的VCC PIN為內部所有邏輯線路的唯一電源,無論是內部CONTROL 機制、H/L SIDE MOSFET的驅動皆需由此做為供電。此時,外掛在VCC外部的電容的遠近,就會影響到VCC的準位。

當我們需要選擇高輸出電流的POL時,其VCC 穩壓電容的位置,就更加格外重要。因為能輸出高電流的產品,其內部CONTROL機制與內部MOSFET的規格都會是屬於高規格的產品。POL除了PACKAGE的設計以外,其搭配的MOSFET也是被精挑細選過的。因為這類高集成的產品,PACKAGE所能承受的瓦特數是固定的,要能輸出高電流的產品,一定要減少PACKAGE內部元件的發熱量,所以內部的MOSFET會選擇超低RDS(ON),當RDS(ON)越低,其DRIVER 電流也相對是較大。

當在連續輸出時,其內部CONTROL 線路需要吃電,內部的MOSFET也需要DRIVER電流、保護線路也一併在偵測,這些所需的電源皆由VCC PIN外的電容做為供電來源。如果,電容擺放的位置,離VCC PIN較遠,那VCC 的準位就會偏低,而UVLO 保護機制就有機會被啟動,造成POL進入保護狀態。

所以,VCC 的電容,我們都會建議放在緊鄰VCC PIN,以確保VCC 供電的穩定。

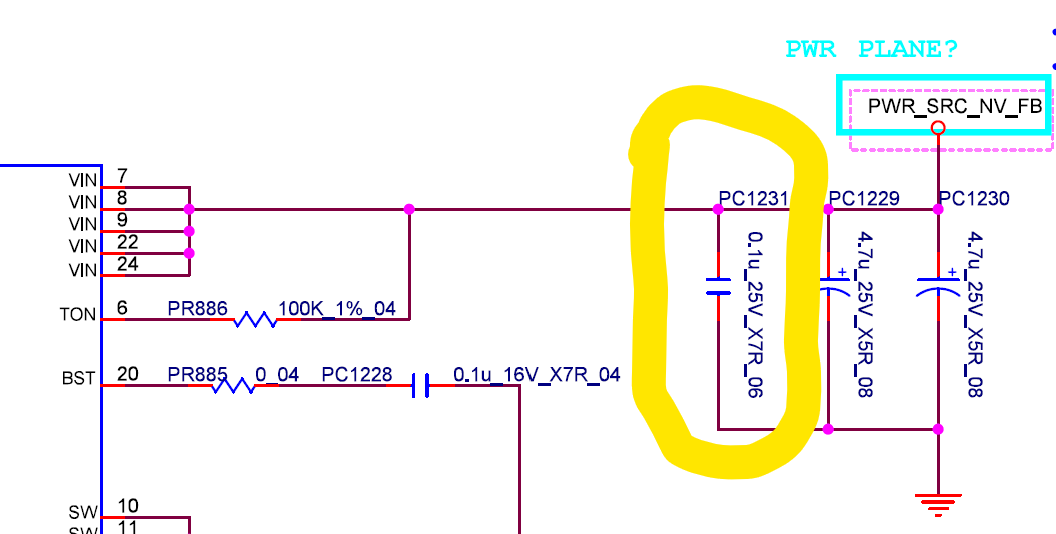

- VIN 濾波電容的處理:

以目前消費產品來看,多以輕薄短小為主,但在有限的板材空間下,各組POWER及相關訊號多為緊緊相鄰。而POL產品在運作時,PHASE 的SWITCHING RING會透過H/S MOSFET TURN ON的通道,影響到VIN 端的POWER PLANE。

有鑑於此,一般在POL 線路設計時,會建議在VIN端輸入電容最靠近POL端增加0.1uF的濾波電容,藉此吸收SWITCHING RING的高頻訊號,以防止干擾到其他共用VIN POWER PLANE端的相關訊號。造成其他訊號的不穩定。

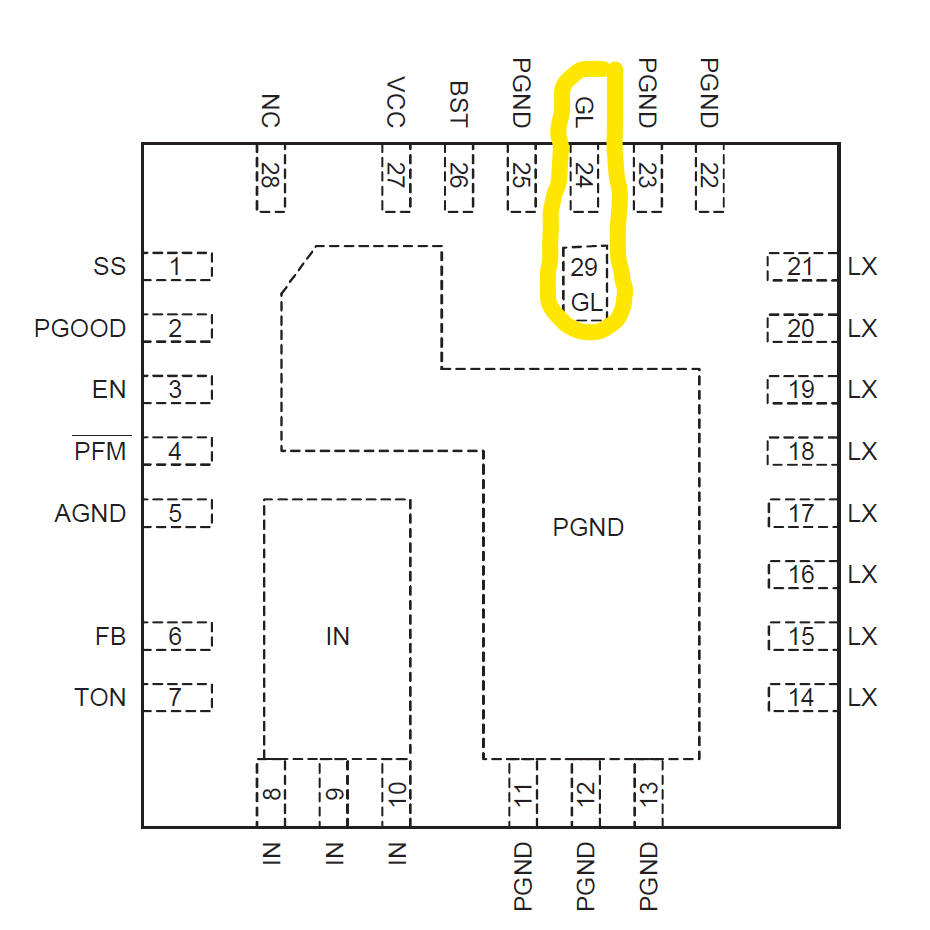

- POL底部LOW SIDE GATE 的處理:

以AOS AOZ2369QI (27A solution)為例,其POL的LOW SIDE GATE一共有2 PIN,除了24 PIN以外,另外在IC底部還有1 個PIN (29 PIN)。以POL零件的設計來看,所有的控制機制,理應全數包在IC內部。而底部的GATE PIN 其實是作為L/S MOSFET 腳架上的一個支撐點。當我們在做LAYOUT設計時,因POL IC的底部,有著兩個大的PAD作為VIN及GND使用,且底部GL PIN較靠近PGND PAD,當GL的PAD在SMT加工稍微偏差時,其較容易與PGND 產生錫橋(solder bridge),當這樣狀況發生時,負責下橋MOSFET驅動的控制單元會因短路的狀況,而產生過大的電流,進而將內部CONTROL機制燒毀。基於上述的情形來看,我們會建議這個PIN腳,不製作PAD做焊接也不上錫。

未完待續……

問與答:

- 以AOS POL產品來看,UVLO是否有容許值?

Ans:以目前AOS POL產品來看,UVLO Typ約為4.2V,且只要一次碰觸到,IC內部就會關閉。

- 以AOS POL產品來看,建議的送電時序為何?

Ans: 一般POL建議的時序為:VIN 先到位,IC VCC再給,EN 訊號最後。

- 以AOS POL產品來看,輸出電壓設定上有無須注意的點?

Ans:以AOS COT 架構的POL來看,首先須注意其Max on time 的限制,再者須注意操作頻率的

設定,這樣就能穩定的輸出。

- 以AOS POL產品來看,過電流保護功能是否可以設定?

Ans:目前AOS POL的產品,OCP有區分為內部自行偵測與可以外部自行設定這兩類。初步可由IC

是否有OCS PIN來做區分。

- 以AOS POL產品來看,建議的操作頻率設定為何?

Ans: 目前AOS POL的產品,一般我們會建議使用在頻率350K ~ 600KHZ左右,這樣的設定在開關損失、傳導損失及PACKAGE 的乘載上較為適宜。