一.硬體平台

SR5E1-EVBE700P評估板支持STMicroelectronics SR5E1xE7微控制器,帶有LQFP 24x24 176L EXPOSED PAD DOWN封裝。評估板是一個獨立的單元,允許訪問CPU、I/O引腳以及任何板外圍設備。評估板適用於工作檯/實驗室,並使用常溫指定組件進行設計。

有關Stellar-E1 MCU EVM的更多詳細信息,請參閱“UM2968,SR5E-EBE7000P評估板用戶手冊”。

二.CLLC PFM+phase shift模式介紹

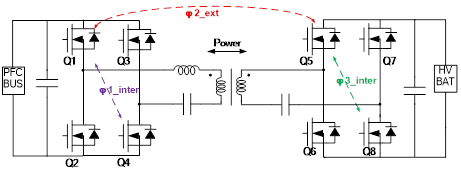

雙向DC/DC(BDC)變換器在電動汽車OBC應用中發揮著重要作用。串聯諧振變換器拓撲結構CLLC由於可以實現零電壓開關(ZVS)和整流二極體零電流開關(ZCS)而得到廣泛應用。由脈衝頻率調製(PFM)控制的CLLC具有電壓增益範圍窄的缺點。為了克服這一問題,採用了PFM和相移的混合控制。

電源拓撲PFM和相移控制要求簡述:

•所有通道的脈衝頻率調製(PFM)和所需的新頻率同步更新

•Q1和Q4內部相移φ1_inter和相移方向固定在電流功率傳輸方向下,φ1_inters用於電流形狀優化和開關應力降低。

•Q5和Q8內部相移φ3_inter和相移方向固定在電流功率傳輸方向下,φ3_inters用於電流優化和開關應力降低。

•管理功率方向所需的Q1和Q5外部相移φ2_ext和相移雙向配置。

•例如:電池充電模式和Q5滯後Q1,電池放電模式和Q1滯後Q5,相移角定義為*(PWM上升沿延遲)。

•Q1和Q2、Q3和Q4、Q5和Q6、Q7和Q8,在穩態下具有死區時間和固定的50%占空比PWM。

•典型開關頻率100~200kHz

•相移和PWM頻率通常不會在同一PWM周期內發生變化

三.StellarE1應用優勢

本節重點介紹Stellar-E HRTIM外圍設備,如下所示:

•通過其他計時器事件(主計時器或timerX)同步計時器計數器

•計時器本身或其他計時器事件的輸出設置/重置

•在計時器本身或其他計時器重複事件中註冊更新(全局更新)

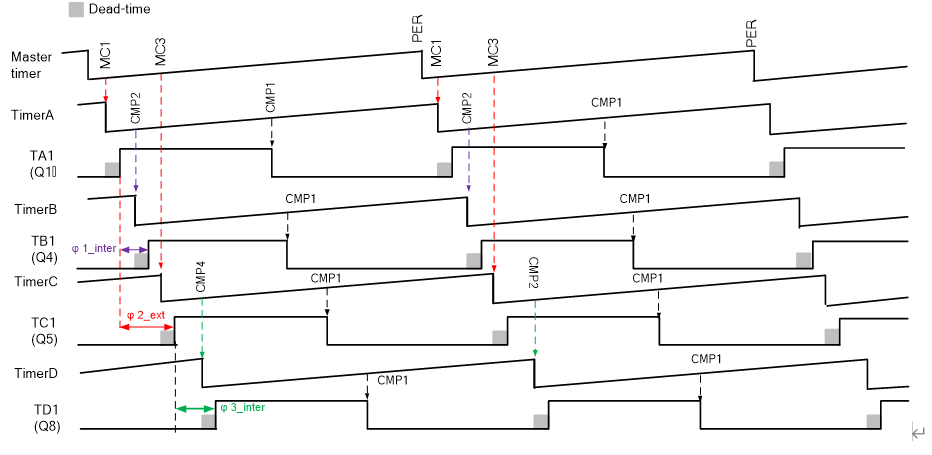

在該解決方案中,主定時器和定時器A、B、C、D用於生成PFM+相移PWM,如圖2所示。Tx1、Tx2輸出由硬體配置為互補PWM和死區插入。

解決方案對系統的好處:

•通過訪問一個寄存器和卸下CPU負載進行相移。

•通過硬體機制實現多定時器同步,更具魯棒性

•通過交換MC1、MC3的相對值實現靈活的相移方向控制

•所有寄存器都可以通過全局同步進行更新(主定時器重置)

•每個定時器計數器重置事件更新的每個寄存器(推薦)

四.HRTIM配置

HRTIM定時器計數器和輸出配置摘要如下表所示,簡要說明:

•用於重置主計數器的主計時器周期匹配。用於設置HRTIM_TA1輸出的Master.CMP1匹配。

•輸出設置/重置事件可能來自定時器本身或HRTIM設置/重置交叉開關的其他定時器,例如TimerA.CMP2設置HRTIM_TB1輸出。

•所有定時器配置為連續模式

•主定時器CMP1、CMP3(MC1、MC3)分別用於重置定時器A、定時器C計數器。因此,定時器A、定時器C時基具有φ2_ext和φ2_ext=abs(MC3-MC1)的相移關係。

•MC1、MC3的相對值控制相移方向,如果功率方向發生變化,交換MC1、MC3的值可以很容易地實現相移方向控制。

•MC3>MC1,φ2_ext>0,Q5滯後Q1;

•MC3<MC1,φ2_ext<0,Q1滯後Q5;

•TimerA.CMP2重置Timer B計數器以控制φ1_inter=TimerA.CMP 2

•TimerC.MP4重置Timer D計數器以控制φ3_inter=TimerC.CMP4

•計時器由按比例變化的Master.CMP1和Master.PER控制的周期。與計時器B、C、D相同。

•通過主定時器重置事件更新主定時器寄存器。

•定時器A寄存器通過定時器A計數器重置進行更新。計時器B、C、D也是如此

五.測試波形

EVM硬體設置如下表所示:

|

scope |

SR5E1 function name |

MCU Pin name |

|

ch0 |

HRTIM1_TA1 |

PE4 |

|

ch1 |

HRTIM1_TA2 |

PE3 |

|

ch2 |

HRTIM1_TB1 |

PE2 |

|

ch3 |

HRTIM1_TB2 |

PE1 |

|

ch4 |

HRTIM1_TC1 |

PD15 |

|

ch5 |

HRTIM1_TC2 |

PD14 |

|

ch6 |

HRTIM1_TD1 |

PD13 |

|

ch7 |

HRTIM1_TD2 |

PD12 |

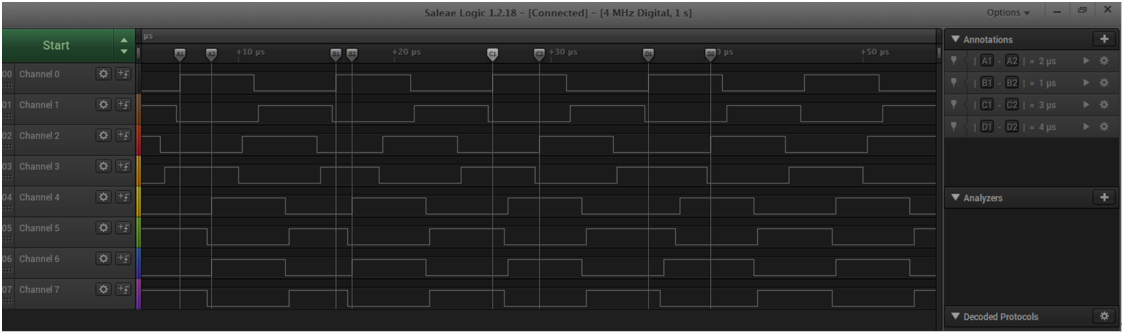

CH0:1 = TA1,2, CH2:3 = TB1,2, CH4:5 = TC1,2, CH6:7 = TD1,2

Tune phase: φ2_ext and φ1_inter

φ2_ext : A1->A2 = 2us, B1->B2 = 1us

φ1_inter : C1->C2 = 3us, D1->D2 = 4us

φ2_ext = MC3 – MC1 (positive phase) or MC1- MC3 (negative phase)

φ1_inter = TA_CMP2 – 0

Tune phase: φ2_ext

φ2_ext : A1->A2 = -1us ,B1->B2 = 2us

評論