電磁干擾(Electromagnetic Interference,EMI)是干擾電纜信號並降低信號完好性的電子噪音,EMI通常由電磁輻射發生源產生。

電磁干擾EMI(Electromagnetic Interference),分傳導干擾和輻射干擾兩種。傳導干擾是指通過導電介質把一個電網絡上的信號耦合(干擾)到另一個電網絡。輻射干擾是指干擾源通過空間把其信號耦合(干擾)到另一個電網絡。在高速PCB及系統設計中,高頻信號線、集成電路的引腳、各類接插件等都可能成為具有天線特性的輻射干擾源,能發射電磁波並影響其他系統或本系統內其他子系統的正常工作。

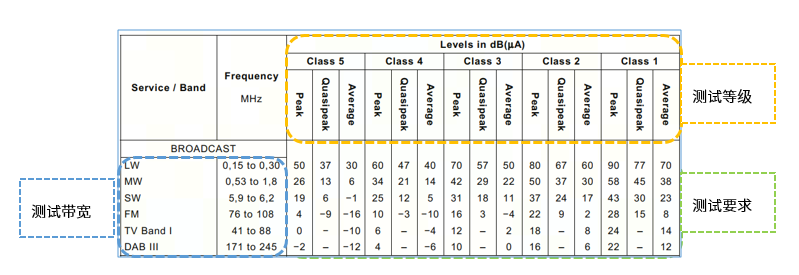

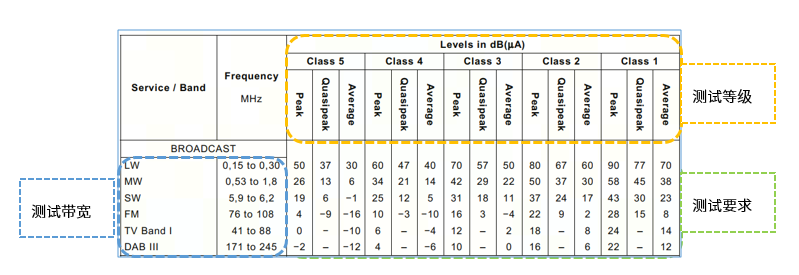

CISPR25《用於保護用在車輛、機動船和裝置上車載接受機的無線電騷擾特性的限值和測量方法》本標準是保護用在車上、船上和裝置上的接受機免受無線電騷擾,規定了限值和測試方法。目前幾乎所有車輛廠商均需求通過此相關標準。下圖為CISPR25測試CEC相關測試標準與要求。

3.D類音頻功放EMI噪聲源

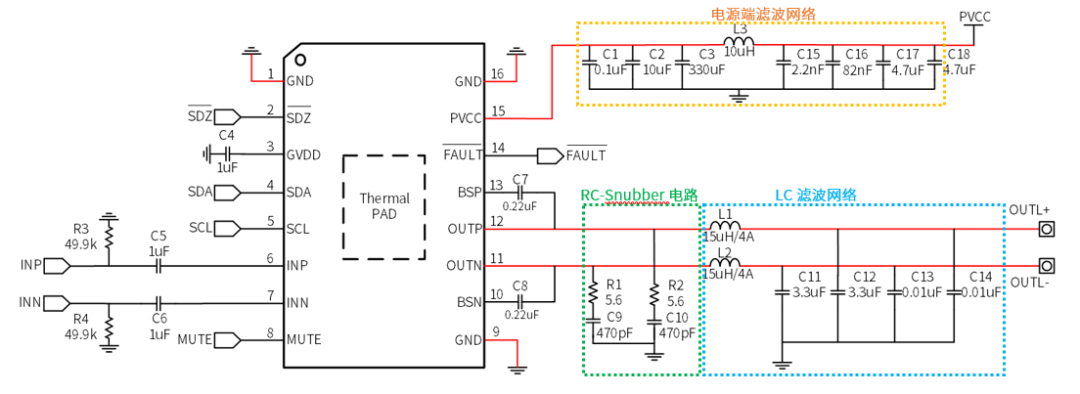

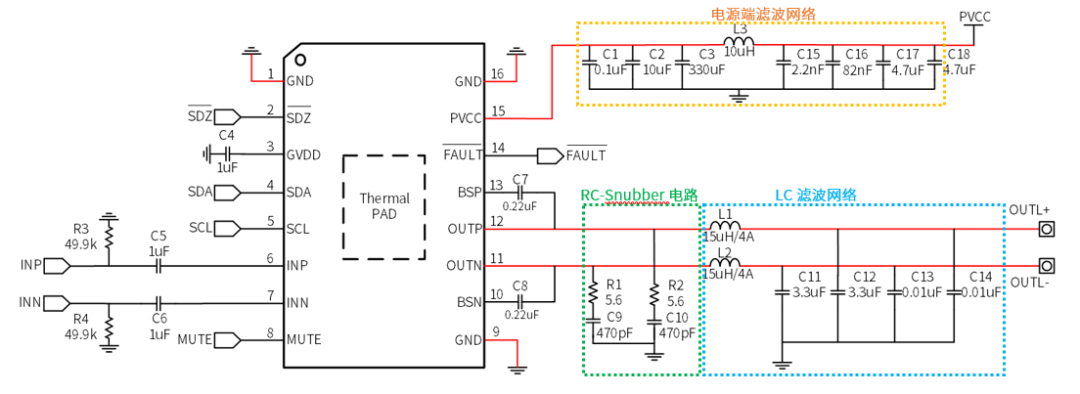

① 典型應用電路

圖2 AW836xxTSR-Q1典型應用圖

② 噪聲源分

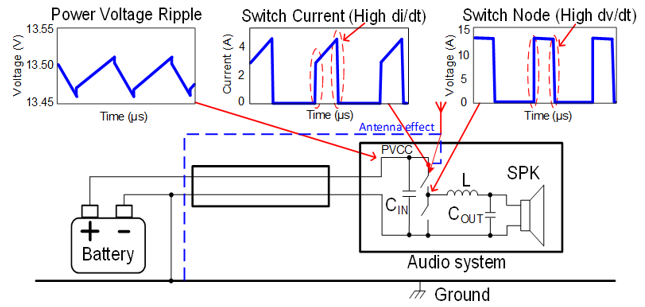

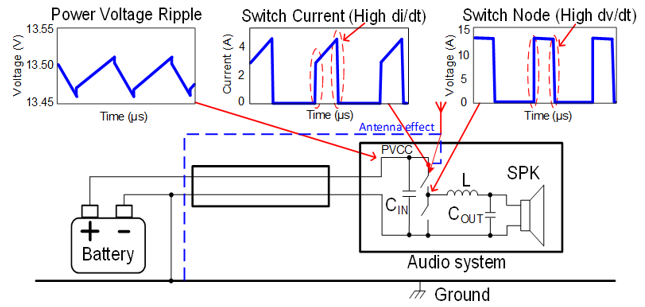

D類功放的EMI的干擾源主要是來自三個地方:

1)工作時開關調製頻率導致的電源上的紋波抖動

2)開關調製過程中大電流隨時間的變化di/dt

3)開關調製過程中電壓隨時間的變化dv/dt

除此之外,整個PCB板器件的布局以及布線對整個電路系統的EMI都會產生影響。下面將在原理圖設計、晶片設計時自身EMI抑制功能、PCB設計分別介紹對EMI的影響分析。

圖3 D類功放噪聲源示意

4. EMI的解決方法

① 原理圖設計

· 電源噪聲濾波網絡設計

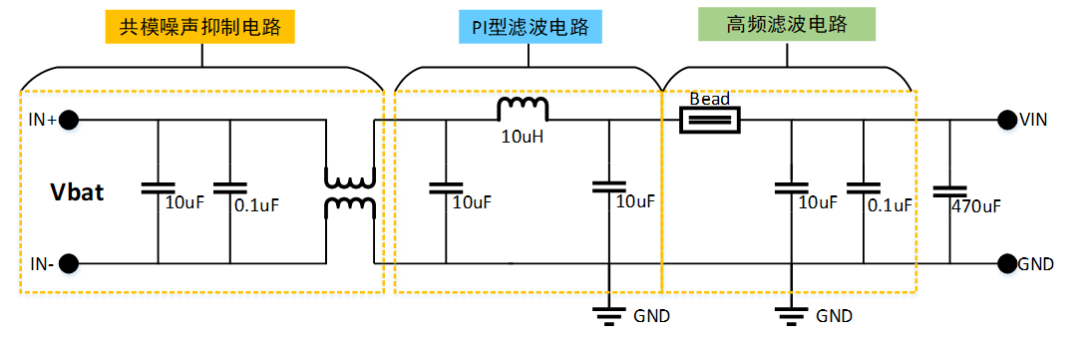

電源網絡噪聲處理常用方式可主要分為以下三種:

1)帶有共模電感的共模噪聲抑制電路

2)Pi型濾波網絡

3)由磁珠與電容構成的高頻濾波電路

具體電路設計可以依據噪聲處理要求進行合理選擇。主要電路結構如下圖所示。

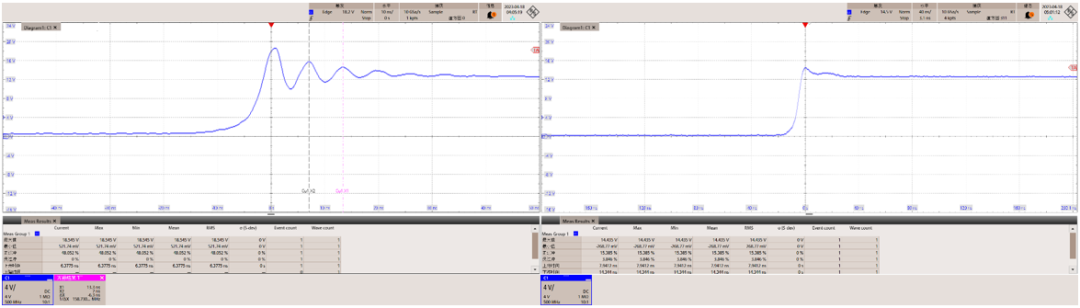

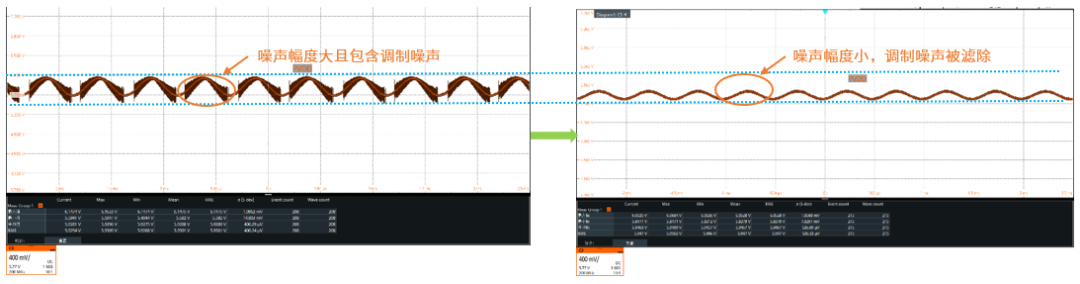

由於D類功放工作時調製產生的電流脈衝會導致PVCC引腳上較大的電壓紋波,若不進行處理將會沿導線傳導至整個電源網絡,如圖4所示AW836xxTSR-Q1電源網絡做了PI型濾波設計,可有效降低電源上的噪聲幅值及高頻干擾,示波器實測波形如下。

圖5 D類調製引入的噪聲

圖6 濾波網絡處理後的噪聲

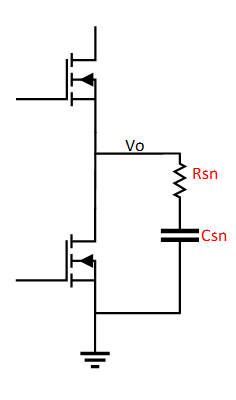

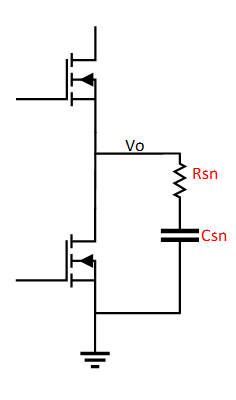

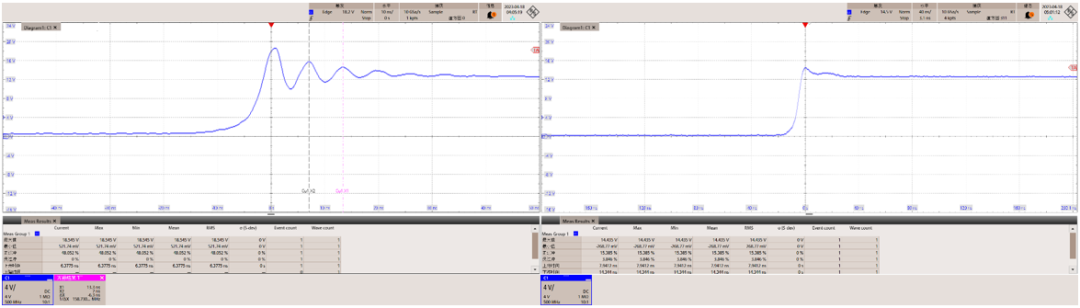

由於晶片引腳,PCB走線,器件雜散參數等寄生參數的存在,高頻開關電路中在開關動作瞬間會產生開關振鈴。振鈴的存在,可能使得開關管承受的電壓超過其耐壓值而發生擊穿;另一方面,開關振鈴為遠超開關頻率的高頻振鈴,會伴隨很高的dv/dt,進而帶來傳導和輻射的EMI問題,所以儘可能地抑制開關振鈴是高頻開關電路設計中一個重要環節。由電阻電容組成的RC-Snubber電路可以有效抑制振鈴,進而有效抑制EMI。圖7為不加RC-Snubber電路的開關波形,圖8加RC-Snubber電路的開關波形,對比顯示高頻振盪得到明顯改善。

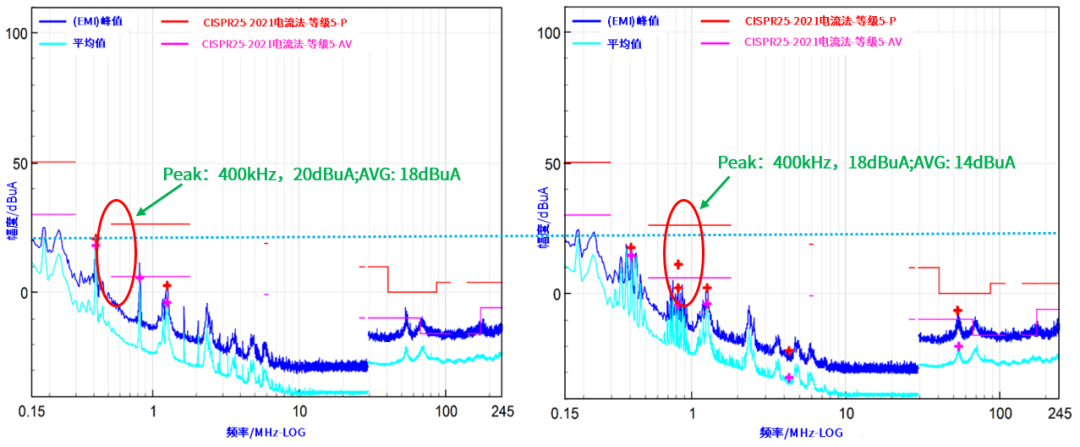

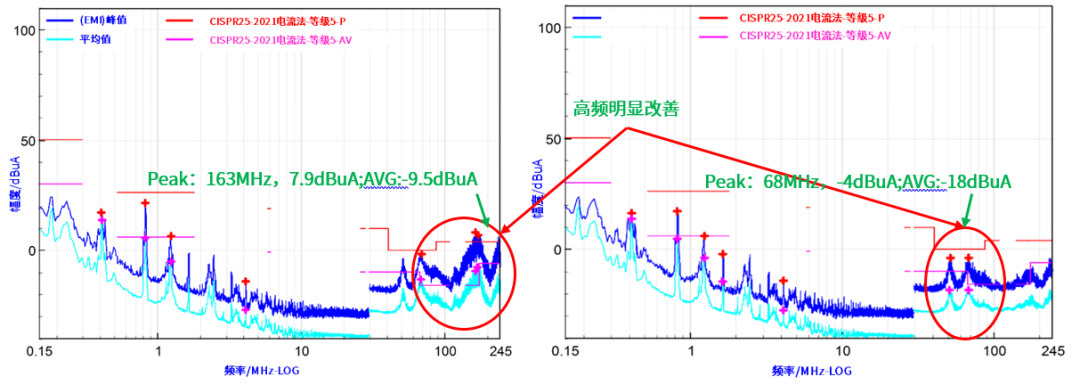

對EMI的影響如圖9,圖10。高頻效果由不可通過CLASS5等級改善為可通過CLASS5,對EMI效果改善明顯。

中大功率音頻設計時,考慮EMI指標往往需要加LC濾波器用於抑制調製信號與高頻噪聲,圖2所示LC濾波電路的截止頻率計算方式如下:

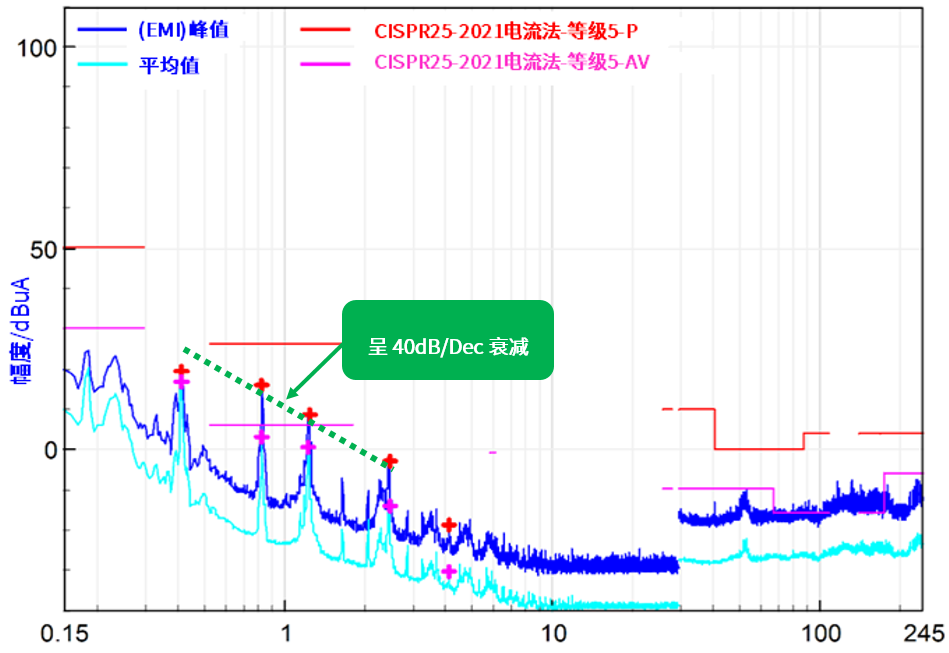

對於低通濾波電路而言,截止頻率外高頻信號將以40dB/Dec進行衰減。

圖11 LC濾波電路對基頻及諧波抑制

② 晶片EMI抑制功能

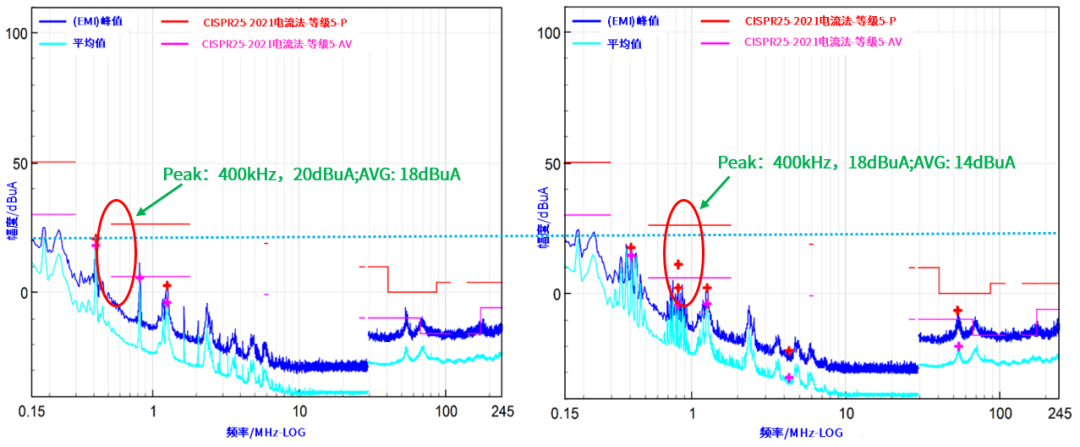

· 調製頻率選擇

基於圖1所示CISPR25測試標準,300k~530k,1.8M~5.9M等頻段並不在測試要求範圍內,AW836xxTSR-Q1系列推出調製頻率為400kHz/500kHz產品,後續將會推出2.1MHz產品(更小的輸出電感與輸出電容,更低的成本),可避免因基波能量落在測試範圍,從而規避基波能量過大而超限的情況。

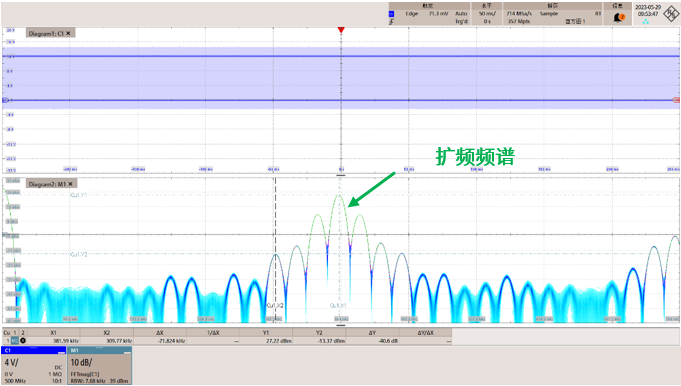

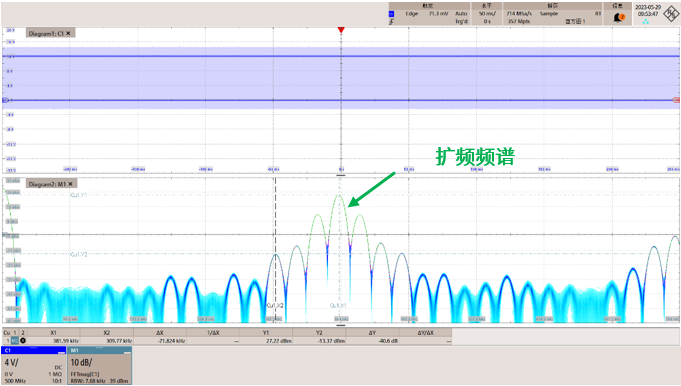

· 擴頻功能

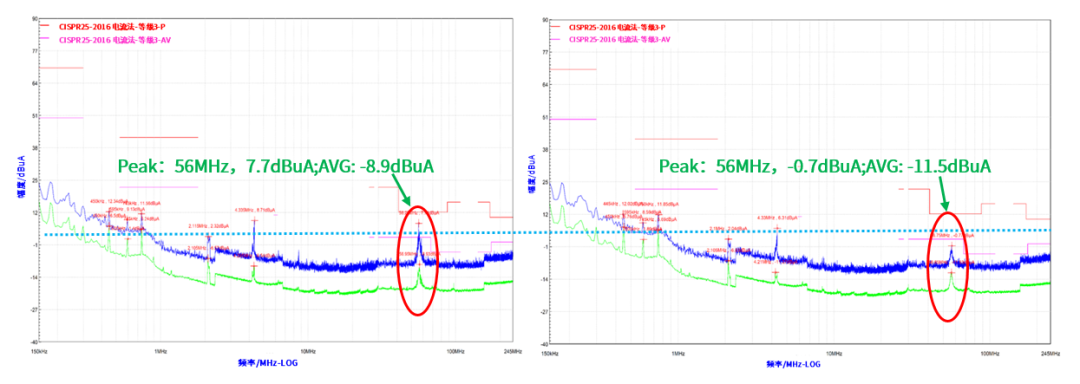

擴頻(Spread Spectrum,SS)是將傳輸信號的頻譜(spectrum)打散到較其原始帶寬更寬的一種通信技術,從而將原始頻帶能量分攤在所擴展的頻帶已降低基頻能量,是EMI抑制常用手段。圖13,圖14對比測試圖展示了擴頻功能對EMI的影響。

圖12 擴頻頻譜

圖13 不開擴頻 EMI測試數據

D類功放輸出邊沿的翻轉帶來大電流隨時間的變化di/dt,電壓隨時間的變化dv/dt;這些都會影響引入高頻噪聲,調沿功能即可以調整邊沿速率,進而降低Δt時間內電流/電壓變化量。

圖15,圖16對比測試圖展示了調沿功能對EMI的影響,高頻處的EMI被明顯優化。

圖16 邊沿調緩 EMI測試數據

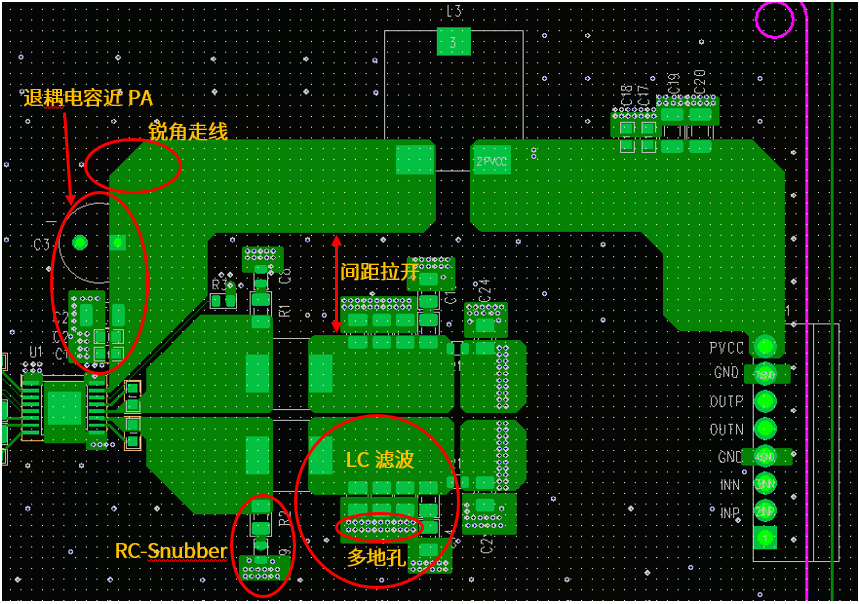

③ PCB設計

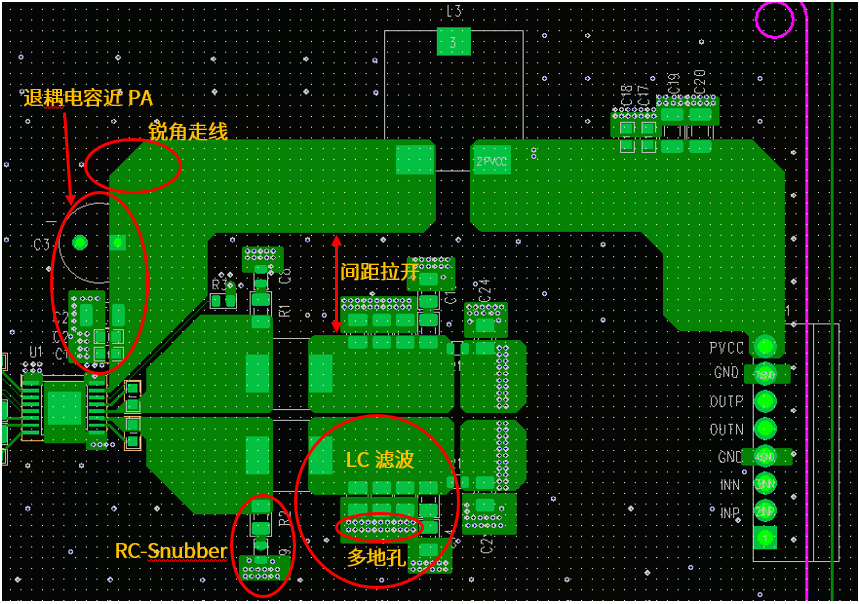

合理的PCB的布局、布線以及器件選型等對EMI影響至關重要,AW836xxTSR主要從電源網絡,輸出功率信號做簡要說明。

2)電源網絡儘量縮短路徑且與系統其他共享電壓網絡呈星形連接,儘量避免菊花鏈形式,避免環路的形成

3)電源網絡與D類功放輸出網絡保持一定距離,避免敏感器件的干擾

5)輸出端的LC濾波網絡及RC-Snubber吸收電路越靠近晶片越好,降低濾波前的網絡長度

6)高頻退耦濾波電容建議靠近PA的PVCC引腳擺放,在最小環路路徑之內擺放,避免高頻去耦失效

7)在L的選型上儘量使用全封閉電感,避免磁泄露導致的磁耦合產生干擾或不必要的損耗

8)電容選用低ESR&ESL型號,電容的地建議就近與主參考地連接,且過孔儘量多,減少過孔帶來的寄生振盪

★博文內容參考自 網站,與平台無關,如有違法或侵權,請與網站管理員聯繫。

★文明上網,請理性發言。內容一周內被舉報5次,發文人進小黑屋喔~

false: https://mp.weixin.qq.com/s/sXpvJPHMEFcHSmLT4Pg1NA

評論