Verilog HDL

行為層次與資料流層次合稱暫存器轉換層次 RTL(Register Transfer Level )

介紹由最高階語法為行為層次,其次為資料流層次,最低階語法為邏輯閘層次。

- 行為層次(Behavior Level)

- 資料流層次(Dataflow Level)

- 邏輯閘層次(Gate Level)

一.首先先介紹最低階的語法_邏輯閘層次(Gate Level)範例

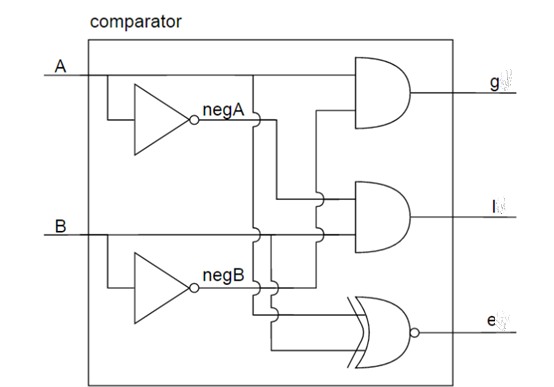

比較器的電路圖

Verilog for Gate Level example: (語法有如畫電路圖一般,使用邏輯寫出硬體描述語言)

module comparator( A, B, g, l, e );

input A, B;

output g, l, e;

wire negA, negB;內部線路宣告

not not1( negA, A );

not not2( negB, B );

xnor xnor1( e, A, B );

and and1( g, A, negB );

and and2( l, negA, B );

endmodule

二.資料流層次(Dataflow Level)範例

Verilog for Dataflow Level example: (語法使用輸出等於輸入(assign),使用運算子&/^寫出硬體描述語言)

module comparator( A, B, g, l, e );

input A, B;

output g, l, e;

assign g= A & ~B;

assign e= ~( A ^ B );

assign l= ~A & B;

endmodule

三.Verilog for Behavior Level example: (procedural assignment,意思是會依照一些程序條件來觸發,又稱作 block assignment,always block 裡面使用的是 blocking assignment,可以很多的blocking 一起同步來運作這時必須使用Clock 宣告正負緣觸發)

module comparator( A, B, gt, lt, eq );

input A, B;

output g, l, e;

always @(*) begin

e = ~( A ^ B );

g = A & ~B;

l = ~A & B;

end

endmodule

評論