經過上篇的分享,我們瞭解了東芝MCU產品所基於Arm® Cortex®-M3內核的基本結構和寄存器分配的細節。接下來下篇帶大家來瞭解Arm® Cortex®-M3內核的操作模式又有哪些技巧!

Arm® Cortex®-M3有兩個特權(特權/非特權)和兩種操作模式(執行緒/處理者)。對於嵌入式使用,可以選擇只有特權級別的基本配置或在特權和非特權之間切換的配置。在特權/非特權級別下,通過在分配給寄存器R13的主棧指標(MSP)與進程棧指標(PSP)之間切換,堆疊區域可由作業系統內核以及使用者常式等處理功能分離和管理。

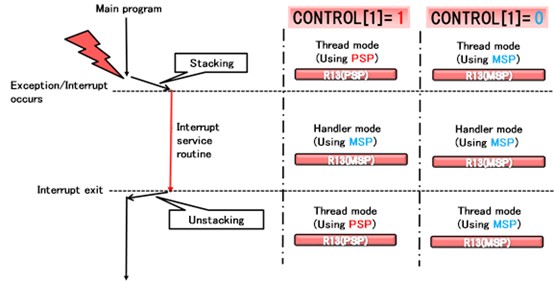

如果發生異常/中斷的程式,控制寄存器的狀態以及堆疊指標的切換情況是怎麼樣的呢?如下圖所示,當發生異常/中斷時,使用中的堆疊會隨控制寄存器CONTROL的狀態而改變。以顯示主棧指標(MSP)和進程棧指標(PSP)之間的切換狀態。

(圖片來源:作者 東芝半導體,網址:https://mp.weixin.qq.com/s/m7O2l8-7Q23Mf4UUMWfdlw)

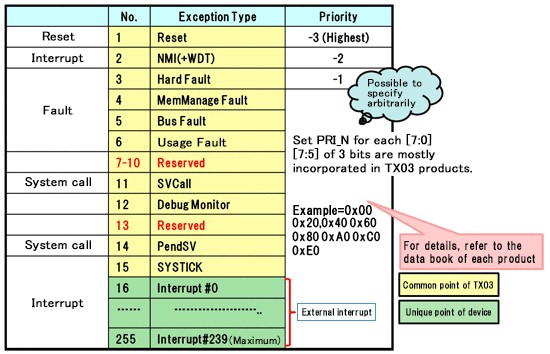

Arm® Cortex®-M3內核的所有異常都在特權模式下運行,且具有中斷特權並支持嵌套中斷,所有異常都集成在NVIC寄存器中。值得注意的是,因每個設備而異,部分設備中斷過程支援外部中斷。異常可通過重定、中斷、故障和系統調用執行。異常類型和特權級別如下圖所示。

(圖片來源:作者 東芝半導體,網址:https://mp.weixin.qq.com/s/m7O2l8-7Q23Mf4UUMWfdlw)

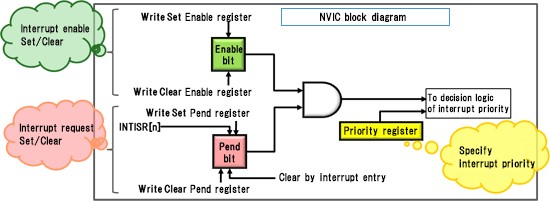

對於集成異常的NVIC控制寄存器,當發生異常和中斷操作時,它作為從主內核到記憶體的設備被訪問,用於控制各中斷使能的設置與清除、控制各插斷要求的設置與清除(釋放保留)以及控制中斷的優先順序。

下面我們再帶大家瞭解NVIC塊的基本功能之一——外部中斷處理控制,將使能位和掛起位分配給每個外部中斷信號,並配置控制寄存器。控制寄存器分為僅設置寄存器和僅清除寄存器。外部中斷的產生通過優先順序寄存器的資訊來控制。該寄存器用於設置中斷優先順序以及使能位元和掛起位元的狀態,如下圖。Arm® Cortex®-M3通過NVIC控制實現高速入棧/出棧處理,此外,如果中斷處理過程中同時發生插斷要求或發生高優先順序的插斷要求,則入棧/出棧處理的寄存器自動保存將被忽略,從而改善處理時間。

(圖片來源:作者 東芝半導體,網址:https://mp.weixin.qq.com/s/m7O2l8-7Q23Mf4UUMWfdlw)

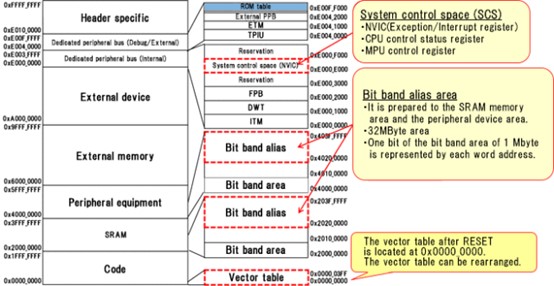

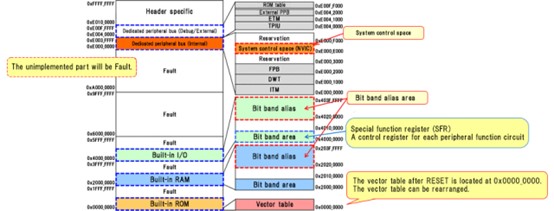

介紹完異常和中斷操作,我們再來看看Arm® Cortex®-M3規格的記憶體映射。下圖一是Arm® Cortex®-M3規格的記憶體映射示意圖,可以清楚看到每個記憶體對應的存儲功能。圖二則展示了這款MCU的記憶體映射細節,從中可以看到相比於Arm® Cortex®-M3標準的規格,該晶片的部分記憶體映射進行了深度優化。

(圖一,圖片來源:作者 東芝半導體,網址:https://mp.weixin.qq.com/s/m7O2l8-7Q23Mf4UUMWfdlw)

(圖二,圖片來源:作者 東芝半導體,網址:https://mp.weixin.qq.com/s/m7O2l8-7Q23Mf4UUMWfdlw)

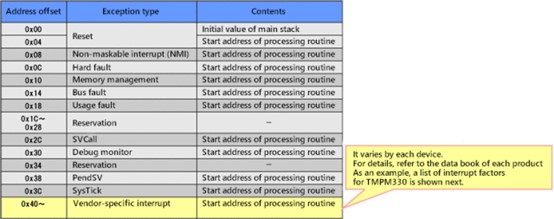

在CPU接收到外部中斷/異常時,它會先查詢向量表,以查找到相應的中斷服務程式位址。向量表是指中斷服務程式入口位址的偏移量與段基址,一個中斷向量佔據4位元組空間。各種異常的處理者(處理常式)的起始位址是分別設置的。當異常或中斷事件發生時,從位址開始獲取異常處理者。各種異常的向量表如下圖所示。

(圖片來源:作者 東芝半導體,網址:https://mp.weixin.qq.com/s/m7O2l8-7Q23Mf4UUMWfdlw)

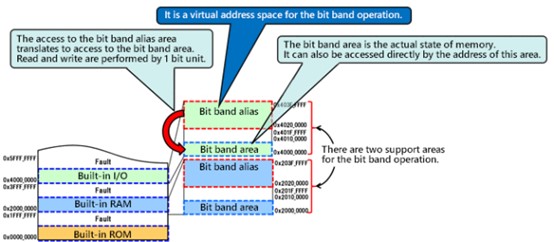

此外,關於位帶和位帶別名區的詳細資訊如下圖所示。記憶體中的資料通過1位元單元進行有效運算。1位元單元通過將位元帶區的資料載入或存儲到位帶別名區來訪問這些資料。那麼位元帶區資料和位元帶別名區的位址如何分配?位元帶別名區的位址以字為單位進行分配(1個字=32位):位帶別名區的字位址bit0訪問位帶區的每個位;位元帶別名區的字位址的分配方式為,每個位址分配給位帶區的每個位。

(圖片來源:作者 東芝半導體,網址:https://mp.weixin.qq.com/s/m7O2l8-7Q23Mf4UUMWfdlw)

上下兩集的簡介,我們深入探討了Arm® Cortex®-M3內核的操作模式,並分析了記憶體映射的具體細節。當然這只是初步的瞭解,而非已獲得了武林密技所以歡迎大家可以透過東芝的官網資訊來找尋適合您的產品應用,及聯繫代理商世平,來為您帶來專業的技術服務喔!歡迎逛逛~

參考來源