一. 概述

本文主要透過 OP-Gyro 方案 Layout,並參考原廠建議 Rules 進行周邊零件擺設,強化訊號完整性,降低 EMI 串擾,使高速訊號透過適當的 Layout 走線,大大提升系統穩定性。

二、介面介紹:

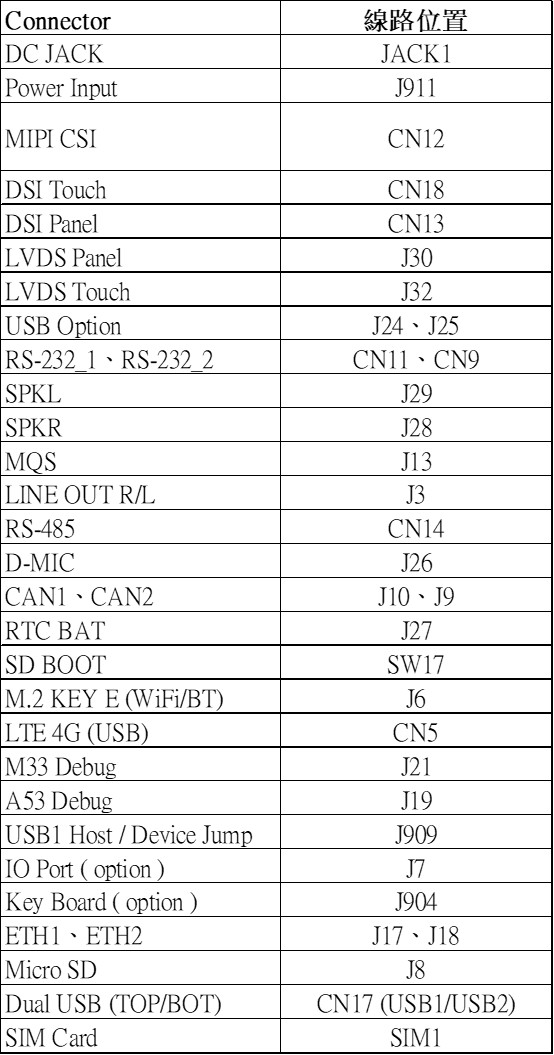

2-1. Board 介紹:

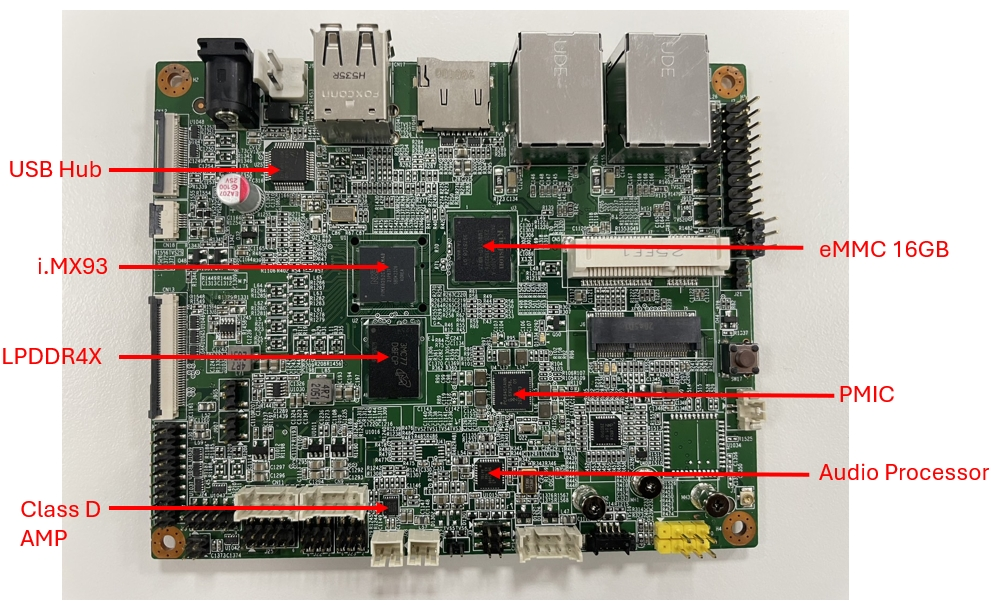

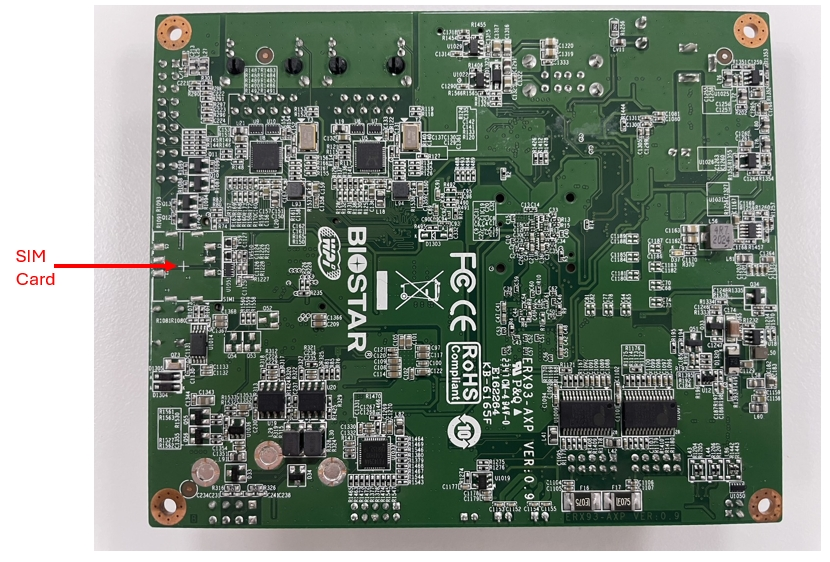

2-1-1. IC Board TOP:

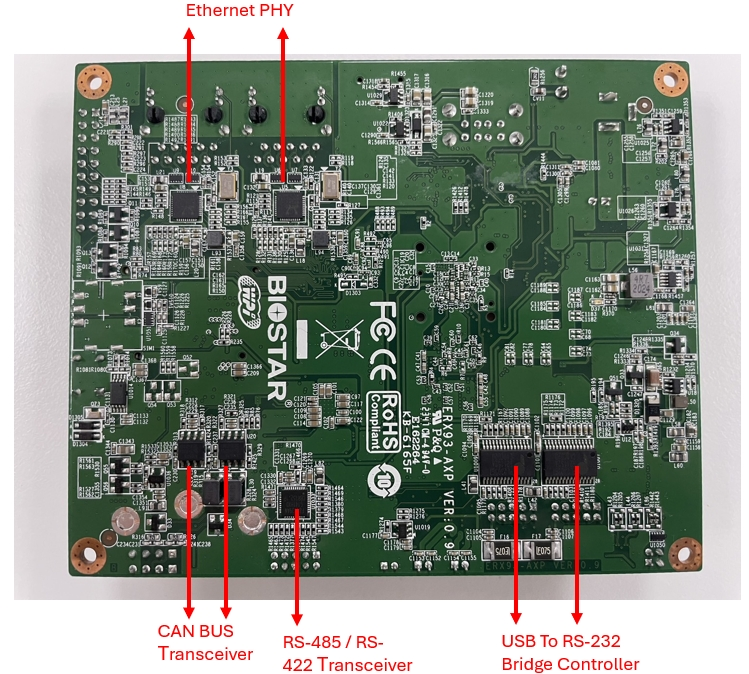

2-1-2. IC Board BOT:

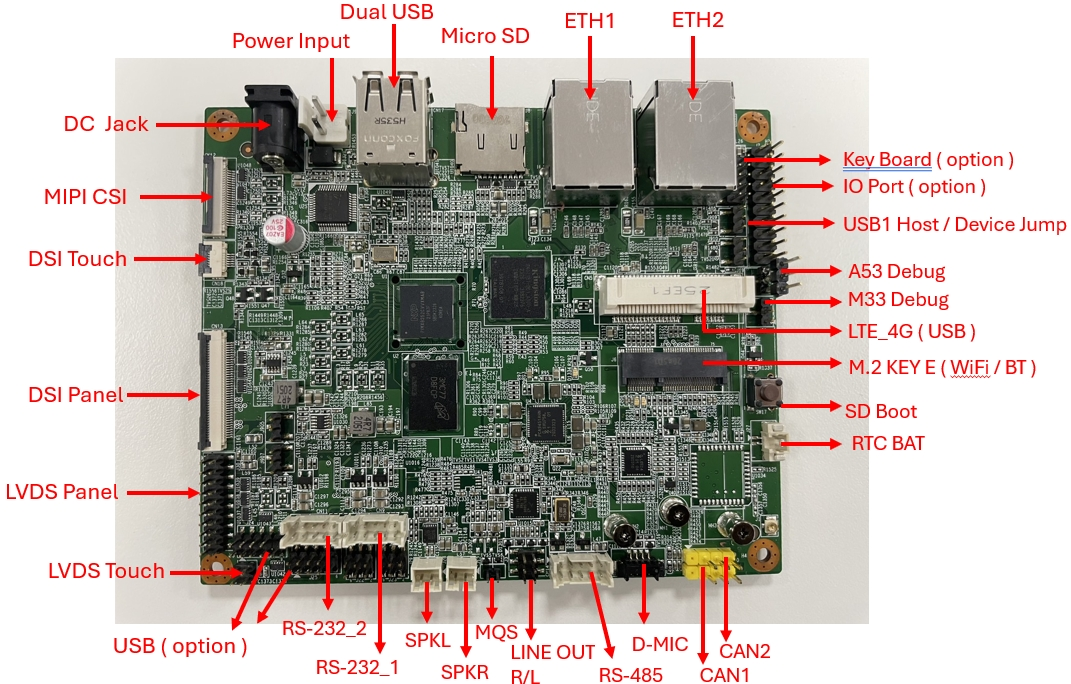

2-1-3. Connector Board TOP:

2-1-4. Connector Board BOT:

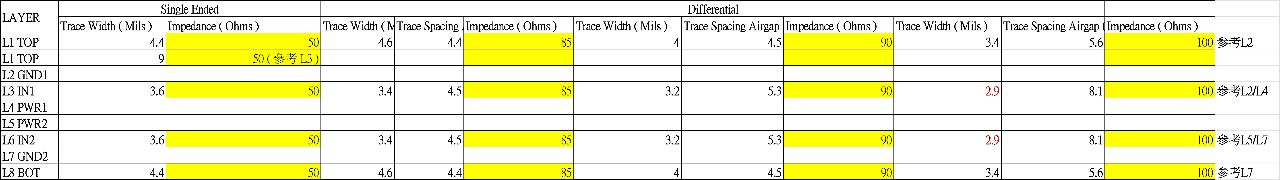

三、PCB 阻抗疊構:

3-1. 阻抗疊構:

四、Layout 注意事項:

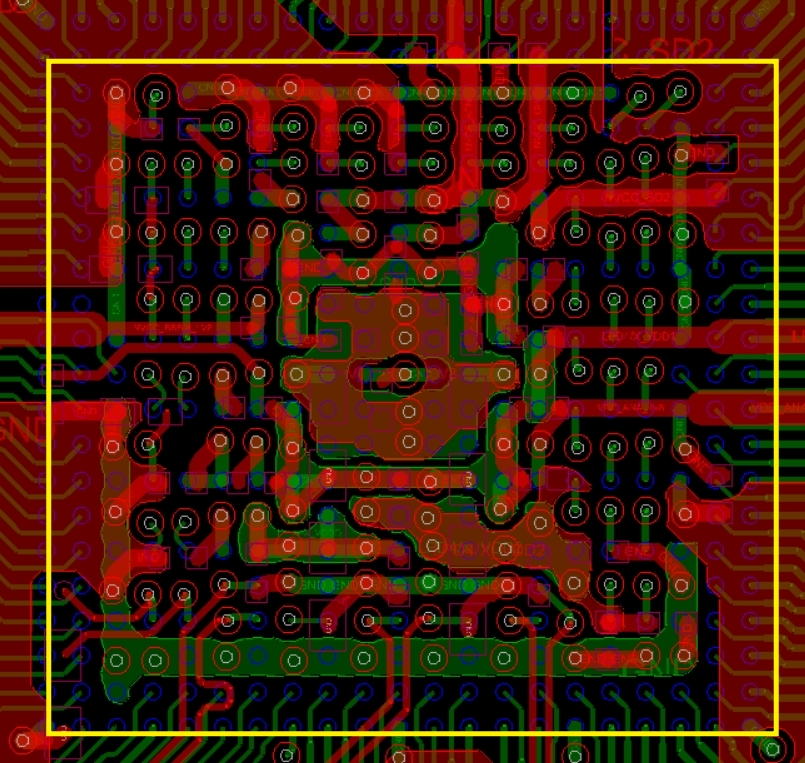

4-1. Decoupling 電容放置說明:

4-1-1. 電容應放置在 PCB 背面 CPU Chip 底部,距離應小於 50mil。

4-1-2. 電容應放置靠近所連接的電源 Pin,並參考線路圖放置,如下圖 。

4-1-3. 電容與電源 Pin 的走線,須走最短路徑,減少電感效應。

4-1-4. 電容直接過孔至 GND,IC 內部 GND 可串接 2 Pin GND 下地如下圖。

4-2. CPU 訊號走線說明:

4-2-1. 疊構設計建議最低為 6 層板,並依序高速訊號 ( 阻抗需求 )、電源、一般訊號進行走線。

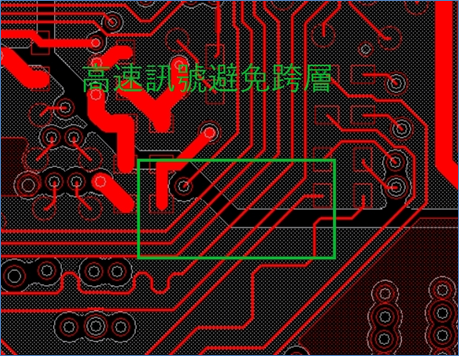

4-2-2. 高速訊號對應層須為完整的 GND,確保訊號不跨層,保持訊號完整性。

4-2-3. 最小走線寬度為 : 3.2 mil,最小線距與 PAD 線距為 : 3.2 mil,最小 Via 尺寸:8 mil, 最小 Via Pad 與 Pad 間距為 4mil。

4-2-5. 高速走線建議可參考 NXP 文件 AN12298。

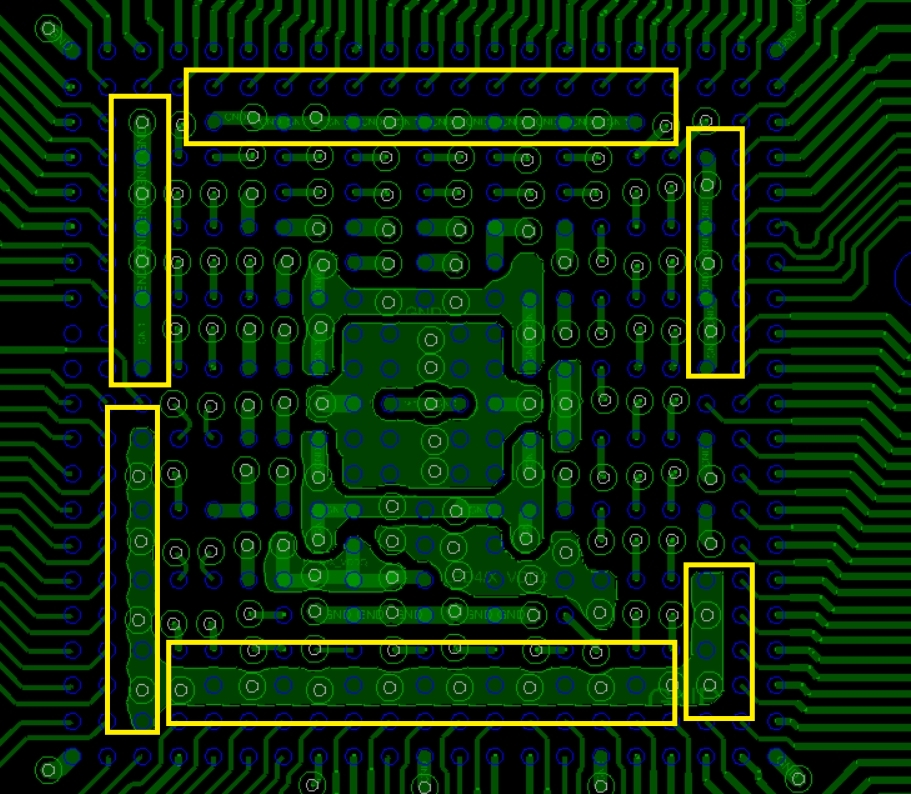

4-3. DDR 訊號走線說明:

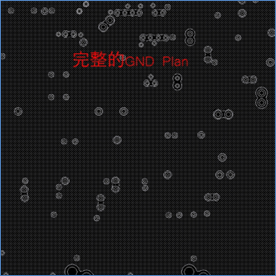

4-3-1. DDR 訊號參考層必須為完整的 GND。

4-3-2. DDR 訊號走線線距不得小於 2 倍線寬,如果空間允許請保持 3~4 倍線寬距離。 EX:如果線寬為 4mil,線與線的距離不得小於 8mil。

4-3-3. DDR 訊號,為了避免串擾產生,須確保 Via 數量不得超過 2 個,並在走線的 50mil 處放置一個 GND Via,可參考 EVB 公板,將第 1 層與第 3 層走單端訊號,差分訊號 CLK、DQS0、1、2、3 可在底層走線,以方便 GND Via 放置。

4-3-4. CLK 和 DQS 信號可以與 DQ / CA 信號在不同層上佈線,DDR 走線應該與其他走線保持 5 倍線距。

4-3-5. CA [ 5:0 ] 腳位不允許 Swapping。

4-3-6. DDR IC 應該放置距離 i.MX93 Main Chip 200mil 處。

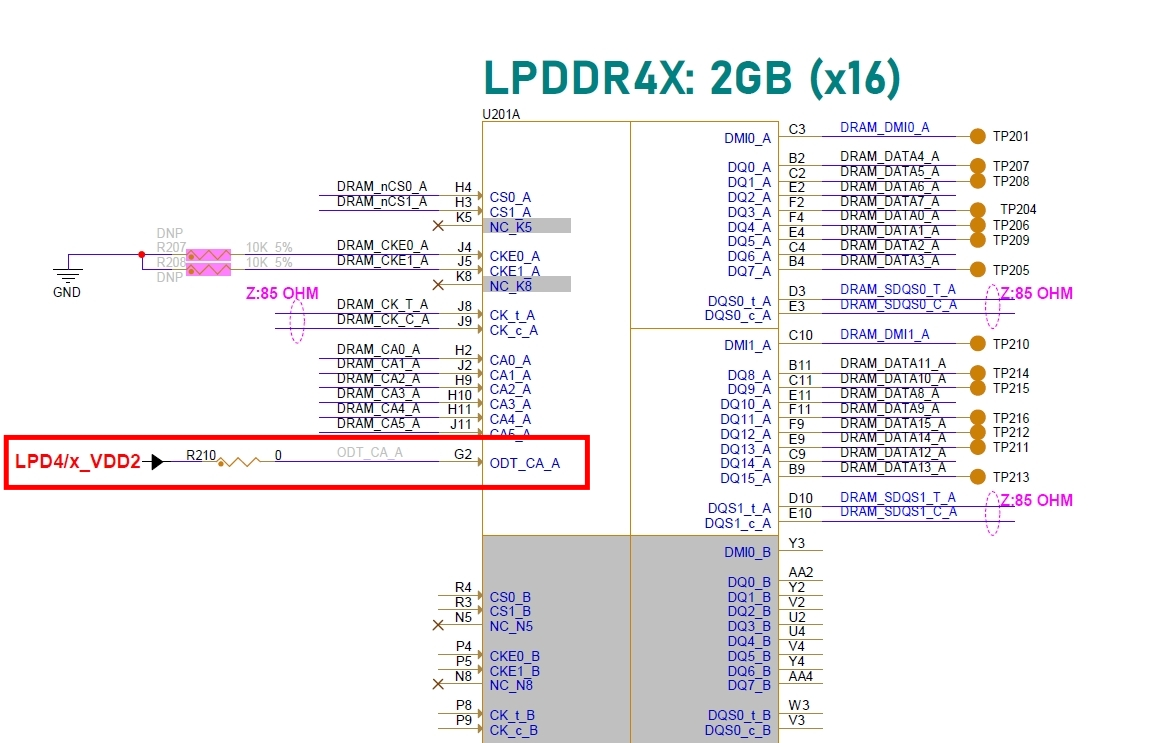

4-3-7. i.MX93 不驅動 ODT_CA 信號,LPDDR4 的 ODT_CA Pin 應連接到 LPD4/x_VDD2,如下圖。

4-4. USB 訊號走線說明:

4-4-1. USB 阻抗需走 90 Ω,盡量避免打 Via,如需打 Via 請少於 2 個。

以上為 OP-Gyro 佈局與 Layout,透過 i.MX 93 Hardware Design Guide,WPI 進而設計出 OP-Gyro EVM 平台,從零件佈局、阻抗疊構,高速訊號 Layout,產出此份文件可以讓各位讀者所設計的平台,提高訊號完整性,降低 EMI 串擾,讓設計出來的方案,能夠更加穩定運行,如果有任何問題,歡迎各位讀者在下面留言討論喔。

參考文件:

- OP-Gyro_Quick_Start_Guide_Weilly_20240417

- 製版說明 - P23-012_OP-GYRO-A1.0_Sam Yang_20231116

- i.MX 93 Hardware Design Guide

- iMX93-A10.Brd

評論