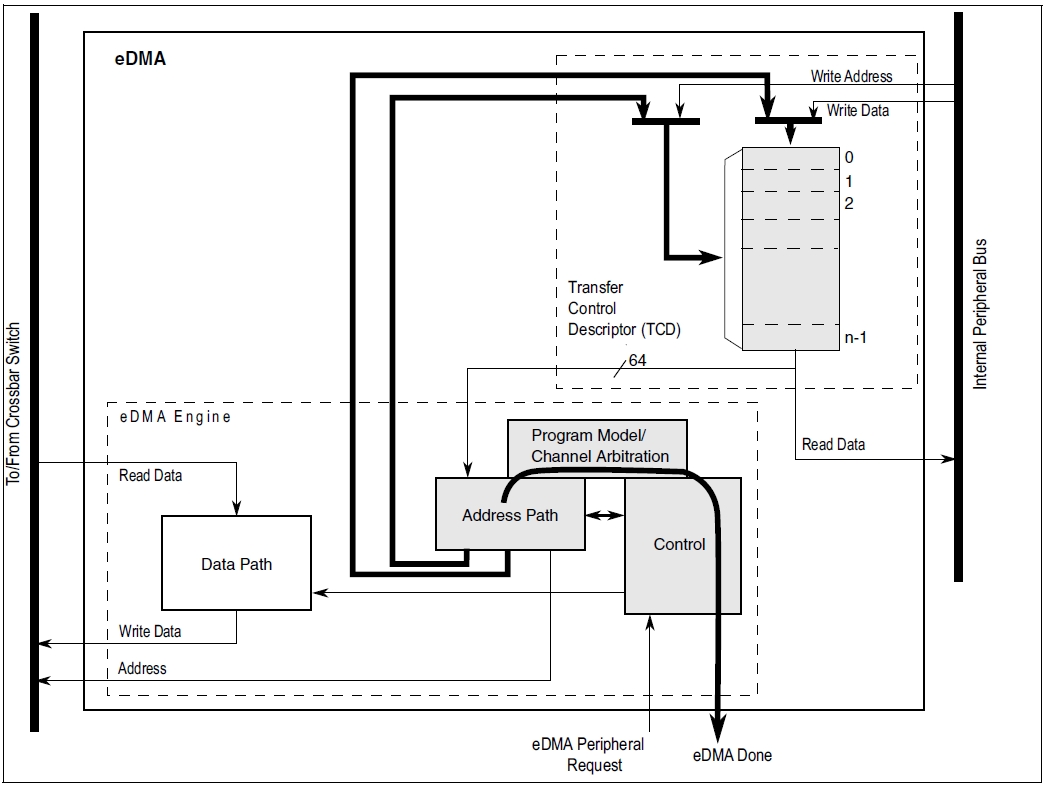

SPC58中使用的增強型直接內存訪問(eDMA)控制器是第二代模塊,能夠在最小的主機處理器干預下執行複雜的數據傳輸。硬體微體系結構包括一個DMA引擎,它執行源地址和目標地址計算,以及實際的數據移動操作,以及包含64個通道中每個通道的傳輸控制描述符的本地內存。

圖1演示了eDMA模塊。

圖1.eDMA框圖

特徵:

eDMA是一種高度可編程的數據傳輸引擎,可以最大限度地減少主機處理器的干預,它旨在用於要傳輸的數據大小是靜態已知的,而不是在數據包本身中定義的應用程序。eDMA模塊的特點:

- 數據移動通過雙地址傳輸:從源地址讀取,寫入到目標地址:

- 可編程的源地址、目標地址和傳輸大小,加上支持增強的尋址模式。

- 64通道實現,執行複雜的數據傳輸和主機處理器最小的干預。

- 內部數據緩衝區,用作臨時存儲,以支持16和32字節的突發傳輸。

- 連接到交叉開關總線控制數據移動。

- 傳輸控制描述符(TCD)被組織為支持兩層深的嵌套傳輸操作。

- 每個通道的32字節TCD存儲在本地內存中。

- 由一個小字節傳輸計數定義的內部數據傳輸循壞。

- 由一個主疊代計數定義的外部數據傳輸循壞。

- 通過以下三種方法之一激活通道:

- 顯示軟體初始化。

- 通過通道對通道鏈接機制發起連續傳輸。

- 外設節奏硬體請求(每個通道一個)。

- 固定優先級和輪詢通道仲裁。

- 通過可選中斷請求報告通道完成情況。

- 每個通道一個中斷,可選地在主疊代計數完成時使能 。

- 每個通道的可選錯誤終止,並在邏輯上加在一起形成一個錯誤中斷到中斷控制器。

- 可選支持分散 / 收集DMA處理。

- 支持複雜的數據結構。

- 支持通過軟體取消傳輸。

二、操作方式

eDMA支持以下操作模式。

- Normal mode

在正常模式下,eDMA在源和目標之間直接傳輸數據。源和目標可以是內存塊或能夠與eDMA一起操作的I/O塊。服務請求啟動傳輸在傳輸控制描述符(TCD)中指定的特定字節數(NBYTES)。小循環是每個服務請求傳輸這些NBYTES的讀寫操作序列。每個服務請求執行主循環的一次疊代,該循環傳輸NBYTES的數據。

- Debug mode

DMA操作可以在調試模式下通過控制器進行配置:

- 如果CR[EDBG]被清除,DMA繼續運行。

- 如果設置了CR[EDBG],則eDMA停止傳輸數據。如果在通道處於活動狀態時進入調試模式,eDMA將繼續運行,直到通道退出。

- Wait mode

在進入等待模式之前,DMA嘗試完成它當前的傳輸。傳輸完成後,設備進入“等待”模式。

三、eDMA初始化

典型的eDMA初始化順序如下:

- 如果不需要默認配置,則寫入CR寄存器。

- 如果需要使用預設配置以外的配置,則將通道優先級級別寫入DCHPRIn寄存器。

- 如果需要,在EEI寄存器中啟用錯誤中斷。

- 為每個可能請求服務器的通道寫入32字節的TCD。

- 通過ERQ寄存器啟用任何硬體服務請求。

- 通過軟體(設置TCDn_CSR[START]位)或硬體請求通道服務(從設備使能其eDMA外設請求信號)。

在任何通道請求服務之後,將根據寫入程序員模型的仲裁和優先級選擇執行通道。eDMA引擎將所選通道的整個TCD,包括TCD控制和狀態欄位(如表1所示)讀入其內部地址路徑模塊。在讀取TCD時,除非檢測到配置錯誤,否則將內部總線上啟動第一次傳輸。從源(由源地址TCDn_SADDR定義)到目的(由目的地址TCDn_DADDR定義)的傳輸一直持續到傳輸了指定的字節數(TCDn_NBYTES)。傳輸完成後,eDMA引擎的本地TCDn_SADDR、TCDn_DADDR和TCDn_CITER被寫回主TCD內存,如果啟用,則執行任何小環路通道鏈接。如果主循環耗盡,則在啟用後執行進一步的後處理(中斷、主循環通道鏈接和分散/收集操作)。

表1. TCD控制和狀態欄位

| TCDn_CSR欄位名 | 描述 |

| START | 當使用軟體發起的DMA服務時,顯示啟動通道的控制位(由硬體自動清除) |

| ACTIVE | 指示通道當前正在執行的狀態位 |

| DONE | 指示主迴路完成的狀態位(當使用軟體發起的DMA服務時由軟體清除) |

| D_REQ | 當使用硬體啟動的DMA服務時,在主循環完成結束時禁用DMA請求的控制位 |

| BWC | 用於通道帶寬控制的節流控制位 |

| E_SG | 控制位使能散聚特性 |

| INT_HALF | 當主循環完成一半時使能中斷的控制位 |

| INT_MAJ | 當主循環完成時使能中斷的控制位 |

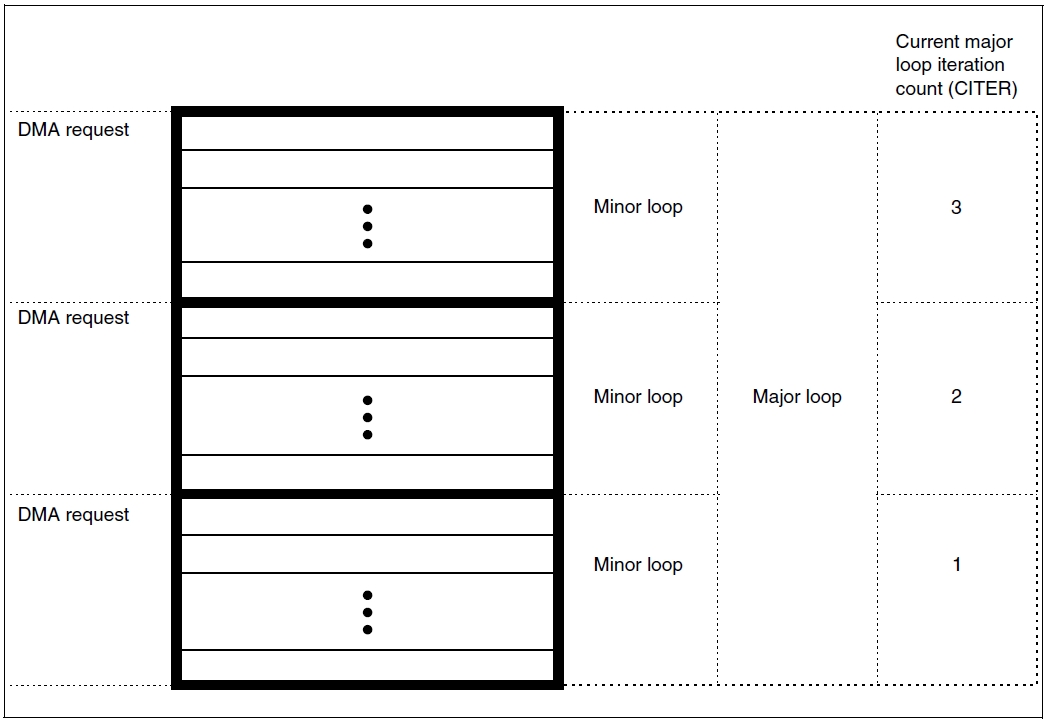

圖2 顯示了每個DMA請求如何在沒有CPU干預的情況下啟動一個小循環傳輸(疊代)。DMA仲裁可以在每個小循環之後發生,並且允許一個級別的小循環DMA搶占。主循環中的小循環的數量由開始疊代計數(BITER)指定。

圖2. 多個循環疊代的示例

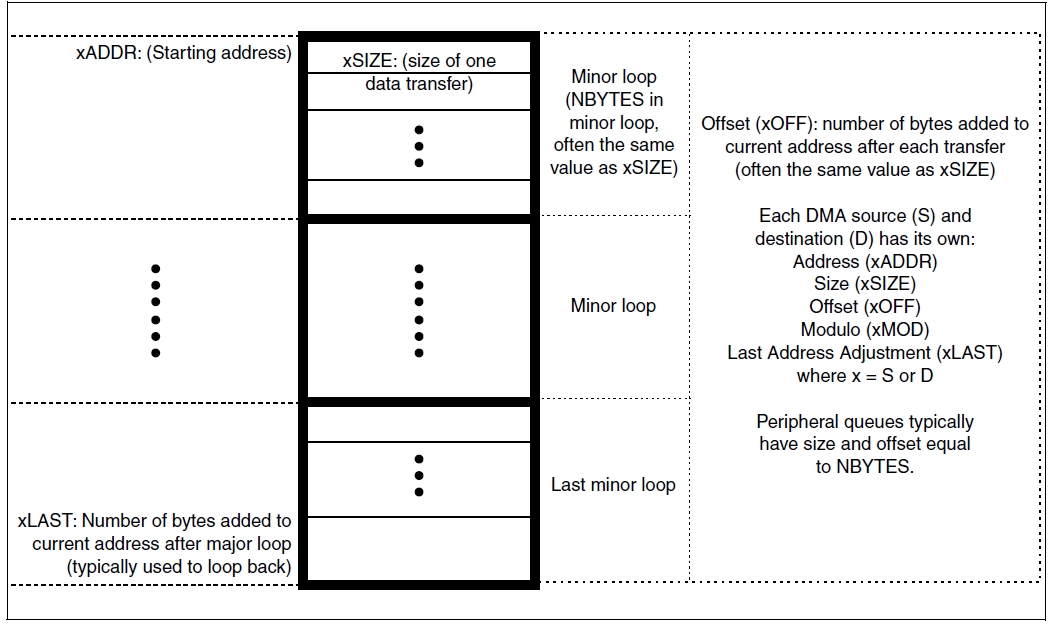

圖3列出了內存數組術語以及TCD設置是如何相互關聯的。

圖3.內存數組術語

四、eDMA傳輸

Single request

要在一次激活中執行n字節數據的簡單傳輸,請將主循環設置為1(TCDn_CITER = TCDn_BITER = 1)。在通道服務請求得到確認並選擇要執行的通道後開始數據傳輸。傳輸完成後,TCDn_CSR[DONE]位被設置,如果正確啟用,則會產生中斷。

例如,下面的TCD表項配置為傳輸16字節的數據。eDMA被編程為主循環的一次疊代,每次疊代傳輸16字節。源內存有一個字節寬的內存埠,位於0x1000目標內存由一個32位寬的埠,位於0x2000。地址偏移量以增量方式編程以匹配傳輸大小:源一個字節,目標四個字節。最終的源地址和目的地址被調整為返回到它們的起始值。

這將生成以下事件序列:

- 用戶寫TCDn_CSR[START]位請求通道服務。

- 該通道由仲裁選擇進行服務。

- eDMA引擎寫:TCDn_CSR[DONE] = 0;TCD_CSR[START] = 0, TCDn_CSR[ACTIVE] = 1。

- eDMA引擎讀取:通道TCD數據從本地存儲器到內部寄存器文件。

- 源到目的的傳輸執行如下:

- 從位置0x1000讀取字節,從位置0x1001讀取字節,從位置0x1002讀取字節,從位置0x1003讀取字節。

- 將32位寫入位置0x2000→小循環的第一次疊代。

- 從位置0x1004讀取字節,從位置1005讀取字節,從位置0x1006讀取字節,從位置0x1007讀取字節。

- 將32位寫入位置0x2000→小循環的第二次疊代。

- 從位置0x1008讀取字節,從位置0x1009讀取字節,從0x100A讀取字節,從0x100B讀取字節。

- 將32位寫入位置0x2008→小循環的第三次疊代。

- 從位置0x100C讀取字節,從位置0x100D讀取字節,從0x100E讀取字節,從0x100F讀取字節。

- 將32位寫入位置0x200C→小循環的最後一次疊代→大循環完成。

- eDMA引擎寫:TCDn_SADDR = 0x1000, TCDn_DADDR = 0x2000, TCDn_CITER = 1 (TCDn_BITER)。

- eDMA引擎寫:TCDn_CSR[ACTIVE] = 0, TCDn_CSR[DONE] = 1, INT[n] = 1。

- 通道退出,eDMA空閒或服務下一個通道。

Multiple requests

除了通過兩個硬體請求傳輸32字節外,下一個示例與前一個示例相同。唯一改變的欄位是主循環疊代計數和最終地址偏移量。eDMA被編程為主循環的兩次疊代,每次疊代傳輸16字節。當通道的硬體請求在ERQ寄存器中啟用後,從設備發起通道服務請求。

這將產生以下事件序列:

- 第一個硬體(eDMA外設)請求信道服務。

- 該通道由仲裁選擇進行服務。

- eDMA引擎寫:TCDn_CSR[DONE] = 0, TCDn_CSR[START] = 0,TCDn_CSR[ACTIVE] = 1。

- eDMA引擎讀取:通道TCDn數據從本地存儲器到內部寄存器文件。

- 源到目的的傳輸執行如下:

- 從位置0x1000讀取字節,從位置0x1001讀取字節,從0x1002,從0x1003讀取字節。

- 將32位寫入位置0x2000→小循環的第一次疊代。

- 從位置0x1004讀取字節,從位置0x1005讀取字節,從0x1005讀取字節0x1006,從0x1007讀取字節。

- 將32位寫入位置0x2004→小循環的第二次疊代。

- 從位置0x1008讀取字節,從位置0x1009讀取字節,從0x100A,從0x100B讀取字節。

- 將32位寫入位置0x2008→小循環的第三次疊代。

- 從位置0x100C讀取字節,從位置0x100D讀取字節,從0x100E讀取字節,從0x100F讀取字節。

- 將32位寫入位置0x200C→小循環的最後一次疊代。

- eDMA引擎寫:TCDn_SADDR = 0x1010, TCDn_DADDR = 0x2010,TCDn_CITER = 1。

- eDMA引擎寫:TCDn_CSR[ACTIVE] = 0。

- 通道退出→主循環的一次疊代。eDMA空閒或服務下一個通道。

- 第二硬體(eDMA外設)請求通道服務。

- 該通道由仲裁選擇進行服務。

- eDMA引擎寫:TCDn_CSR[DONE] = 0,TCDn_CSR[START] =0,TCDn_CSR[ACTIVE] = 1。

- eDMA引擎讀取:通道TCD數據從本地存儲器到內部寄存器文件。

- 源到目的的傳輸執行如下:

- 從位置0x1010讀取字節,從位置0x1011讀取字節,從0x1012讀取字節,從0x1013讀取字節。

- 將32位寫入位置0x2010→小循環的第一次疊代。

- 從位置0x1014讀取字節,從位置0x1015讀取字節,從0x1016讀取字節,從0x1017讀取字節。

- 將32位寫入位置0x2014→小循環的第二次疊代。

- 從位置0x1018讀取字節,從位置0x1019讀取字節,從0x101A讀取字節,從0x101B讀取字節。

- 將32位寫入位置0x2018→小循環的第三次疊代。

- 從位置0x101C讀取字節,從位置0x101D讀取字節,從0x101E讀取字節,從0x101F讀取字節。

- 將32位寫入位置0x201C→小循環的最後一次疊代→大循環完成。

- eDMA引擎寫:TCDn_SADDR = 0x1000, TCDn_DADDR = 0x2000,TCDn_CITER = 2(TCDn_BITER)。

- eDMA引擎寫:TCDn_CSR[ACTIVE] = 0, TCDn_CSR[DONE] = 1, INT[n] = 1。

- 通道退出→主循環完成。eDMA空閒或服務於下一個通道。

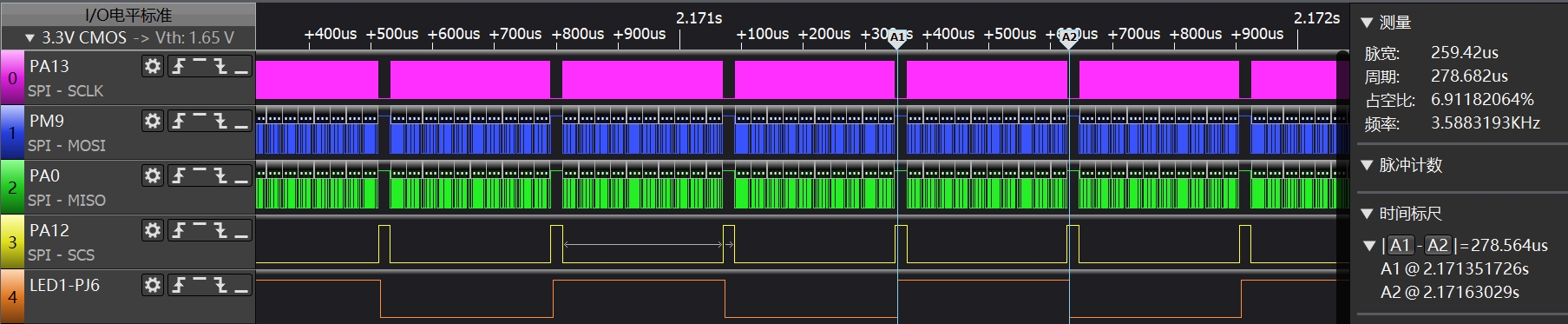

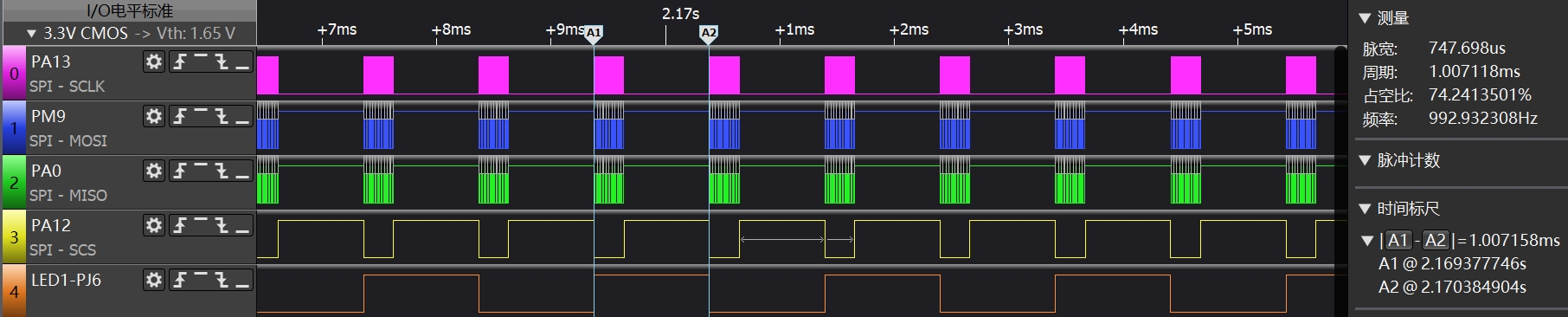

五、eDMA效果測試

測試SPIQ傳輸數據時,在不開啟eDMA的情況下,如果主程序運行周期小於SPIQ傳輸周期,會覆蓋SPIQ傳輸的數據,不能完全傳輸完整的數據串,需要為SPIQ傳輸增加延時,導致主程序不能按照既定的周期運行,開啟eDMA後,傳輸數據不需要一直占用CPU資源,不影響主程序運行周期,傳輸完成後自動進入下一個運行周期。

SPIQ在開啟eDMA時傳輸數據效果如下圖:

圖4.SPIQ開啟DMA傳輸數據效果圖

圖5.SPIQ不開啟DMA傳輸數據效果圖

評論