一. 概述

電子產品工作都離不開電源,電源 DC-DC 模塊應用也越發廣泛,但在產品最終測試 EMC 時, DC-DC 模塊卻成了 EMC 超標的一個重要因素,因此在設計時 DC-DC 的 EMI 噪聲抑制必須引起重視。本文將根據博主實際整改經歷主要介紹 DCDC 模塊噪聲來源並提供一些整改意見,給具有相同 EMI 問題的同仁一個參考。

二. 問題描述

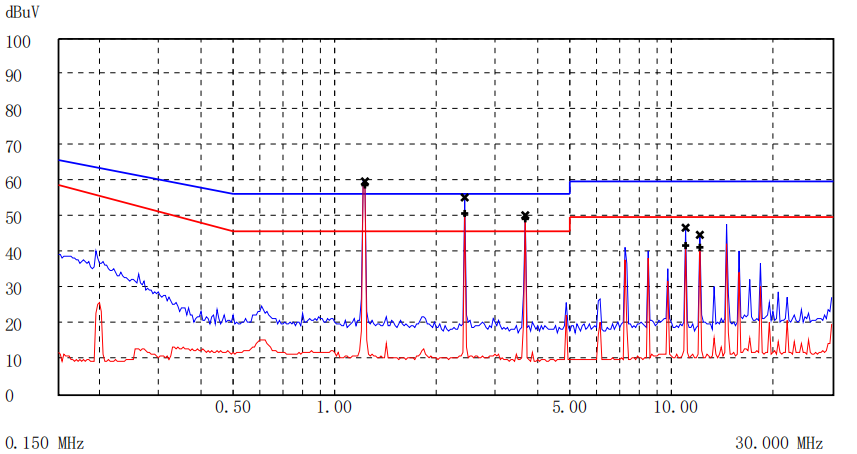

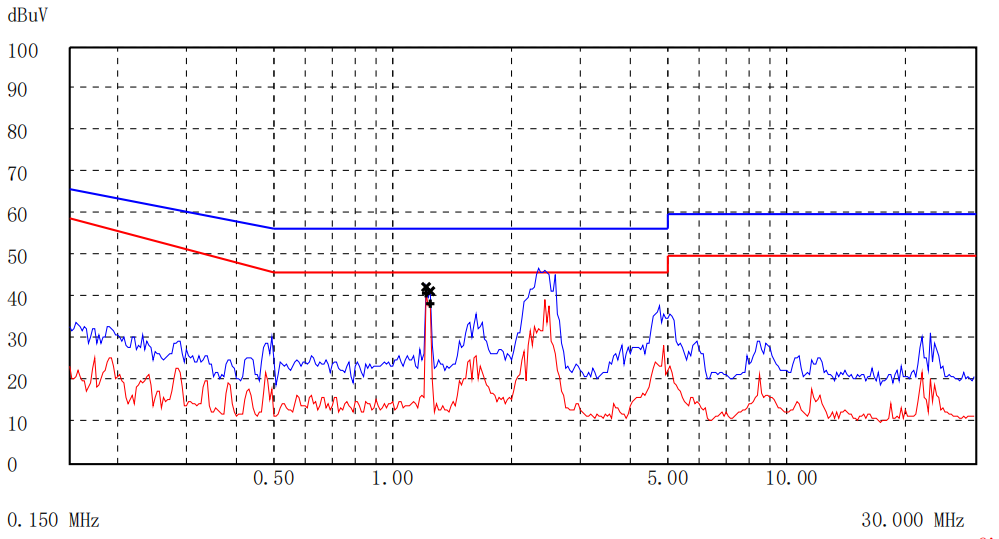

進行 EMI傳導測試時在 1.2MHz、2.4MHz、3.6MHz 左右傳導超標,在 1.2 M 及其倍頻處出現尖峰(測試標準 EN55014)。

三. 問題定位

1. 將外設逐個關閉,測量其傳導。結果在關閉其他外設僅進行供電的情況下其頻段點對應尖峰仍然存在。

2. 單獨啟用 DCDC,測量其傳導。結果測出噪聲頻譜與傳導檢測頻譜基本一致,確認噪聲為 DCDC 模塊導致。

四. 問題分析

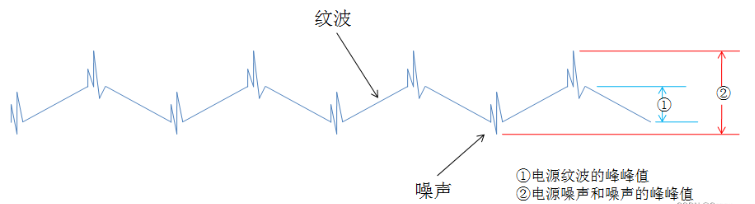

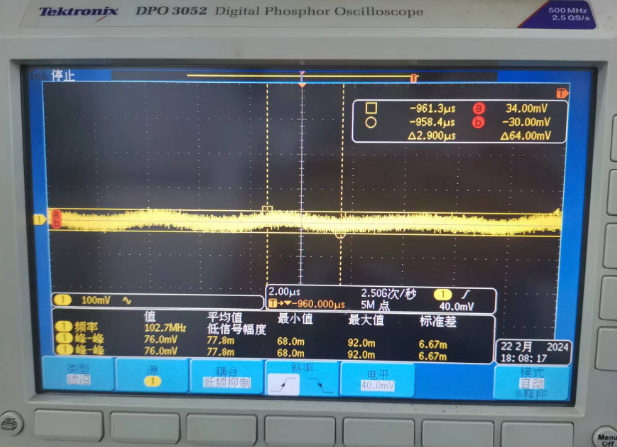

圖 5 是通過示波器測量的 DCDC 紋波時域圖,可以看到並沒有很明顯的開關噪聲幅值

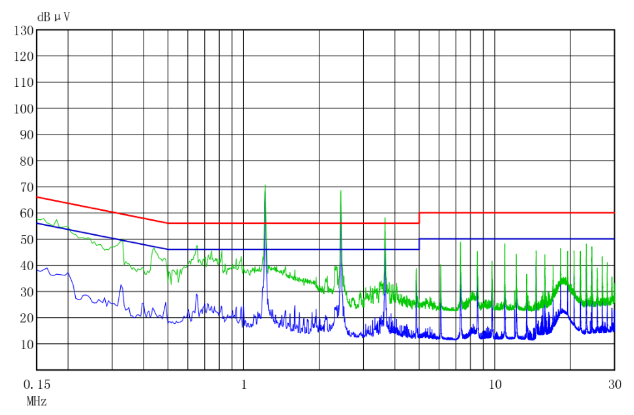

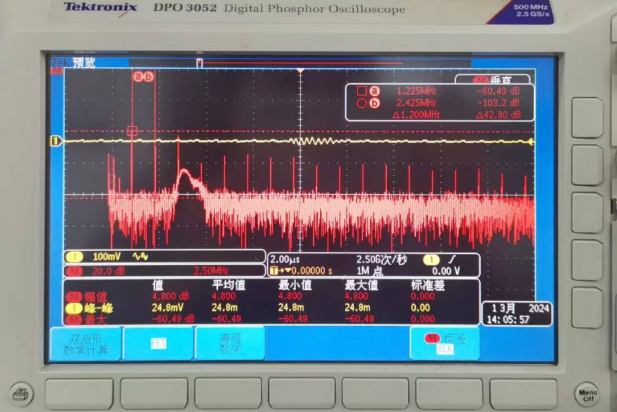

圖 6 是通過示波器測量的電源輸出端的頻譜,在百兆的高頻段未出現高的幅值,出現尖峰的頻率點確實是落在 1.2 M 及其倍頻處。

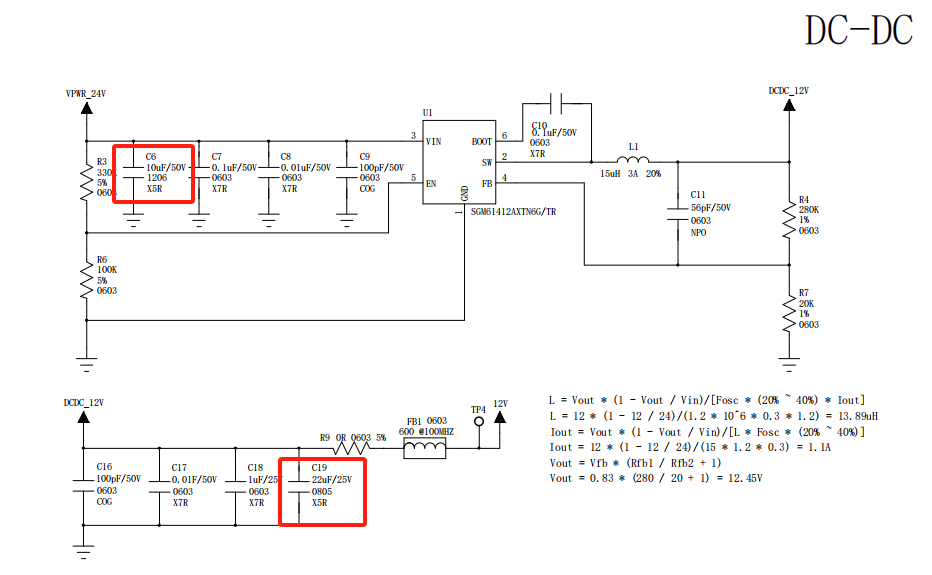

此時確認是由 DCDC 的 1.2MHz 開關頻率引起的紋波電流噪聲,紋波頻率等於開關電源的工作頻率。紋波是開關電源的固有屬性,無法從根本上消除,但它也是一種有規律的、可預測的信號變化,可以通過濾波等方法降低其影響。在 DCDC 晶片的參考設計中通常會加入濾波電容來濾除紋波噪聲干擾,大容量電容濾除較低頻的紋波電流,較小電容可以濾除更高頻率的紋波電流輸出。例如在博主使用的 DCDC 模塊參考設計中就中加入了 22uF 電容來濾除 1.2 MHz 的電流噪聲,並且加入了其餘容值的電容來濾除其他頻段的噪聲。

圖 7 所示是在設計初期加入的濾波電容,已經涵蓋了多段頻率範圍,防止多個頻段的噪聲,那為什麼已經加入了濾波電容,在電源線上仍會有該頻率的尖峰呢?

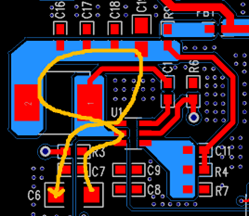

仔細查看博主 DCDC 模塊 PCB 布局會發現問題所在,PCB 設計時在頂層濾波電容及 DCDC 晶片的噪聲電流迴路中出現了交叉及隔斷現象,雖然有在地層進行接通,但由於噪聲的回流不是最短路徑,不一定會按照設想的迴路進行傳輸,濾除後噪聲回到晶片地路徑變長,回流路徑變大,噪聲回到 DCDC 地引腳的路線無法確定,最終噪聲電流通過電源線以差模噪聲和共模噪聲的形式傳輸干擾,表現為傳導超標。

圖 8 噪聲迴路在頂層出現交叉和隔斷

五. 問題解決

1. 選擇合適的電路元件:如選擇具有抖頻展頻功能的晶片,更適合在設計初期考慮使用。

2. 增加吸收迴路:如 RC 吸收電路,更適合濾除由振鈴等導致的高頻信號。

3. 加入磁珠:磁珠的阻抗頻率特性等更適合解決輻射干擾問題。

4. 修改PCB 布局:給噪聲的回流提供更短路徑,減小回流面積是個比較好的方法,最好是在設計初期就考慮,在此例中由於需重新布局,無法確定是否會引入輻射噪聲,因此為進行修改

5. 濾波技術

由 DCDC 產生的噪聲,是經 DCDC 晶片的輸入電路再經線束傳到接收機的,因此要解決此問題可在 DCDC 的輸入路徑上增加濾波電路。

① 加入共模電感及 X 電容,主要濾除共模噪聲,經過測試可濾除大部分噪聲,但成本稍高,取值為經驗值。

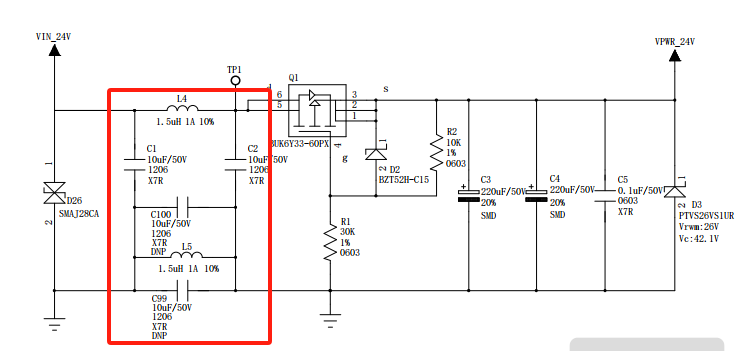

② 加入 LC 濾波電路,本例在總電壓輸入端加入 LC 低通濾波電路

圖 9 加入 LC 低通濾波器

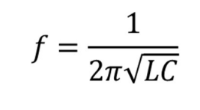

電容和電感取值根據 LC 低通濾波器的截止頻率計算,電容儘量選取在濾除頻率點 處阻抗值低的,電感儘量選取處阻抗值高的:

圖 10 截止頻率

實際的器件選型還需要根據測試的濾除效果和成本進行調整,本例中測得電感值為 1.5uH 貼片電感和 10uF 電容組成的 LC 低通濾波器效果可將 1.2MHz 噪聲減低至法規線以下。

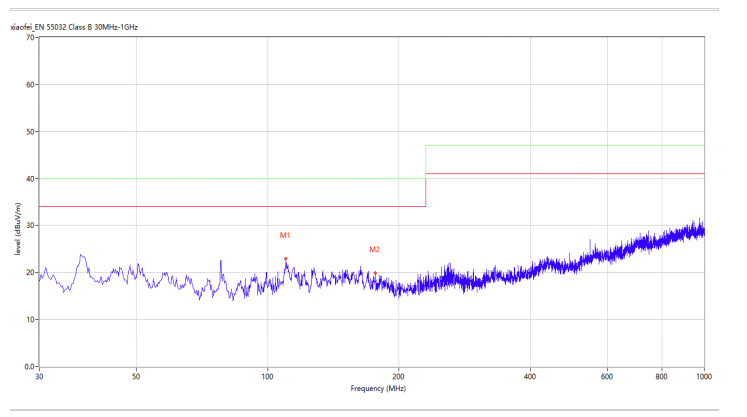

圖 11 整改後檢測機構傳導波形

六. 總結

DCDC開關電源由於其固有的開關特性,成為低頻段噪聲的一個重要來源,因此在電路設計中需要進行重點考慮和處理,在DCDC輸入前端增加濾波電路是一個有效的解決辦法。

評論