1.介紹

Sigma-Delta模數轉換器(SDADC)數字接口控制片上SDADC並保持可用於應用的控制和狀態寄存器。它為廣泛的應用提供了準確的轉換數據。

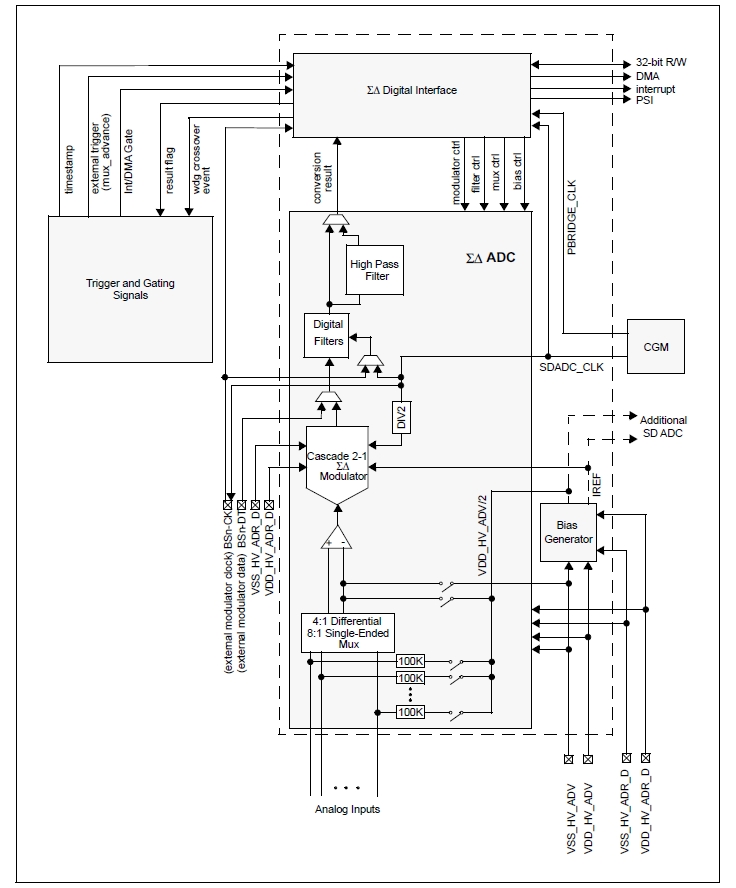

下圖描述了SDADC及其數字控制塊的框圖。SDADC數字接口模塊提供了工作模式選擇(單端或差分)、模擬輸入增益、抽取率、高通濾波器使能等所有控制信息。它還生成用於共模電壓選擇的偏置控制,將正負極偏置到不同的電壓水平(例如,半比例尺偏置,參考地,參考電源)用於診斷。它為所選通道生成模擬多路復用器控制信號。它還提供外部調製器支持,並保持內部調製器在低消耗模式。為了協助跨多個ADC塊的同步操作,實現了硬體觸發支持來啟動數據轉換。

- 16位數據解析度輸出

- 單端輸入或差分輸入操作模式

- 兩種操作模式的可編程環繞機制

- -可配置觸發源:硬體或軟體

- -可配置循環的初始入口和環繞值

- 可配置偏置負輸入終端在單端模式

- 增益和偏移校準支持使用固定偏壓輸入終端

- 可編程抽取率

- 級聯COMB + FIR抽取濾波器,可選FIR濾波器用於SD ADC數據路徑

- 模擬輸入可編程增益

- 可選的外部調製器支持

- 可選的高通濾波器純交流應用

- 硬體觸發器支持多個SDADC塊的同步操作

- 由軟體生成觸發事件輸出

- 可編程FIFO結構存儲16位轉換數據

- 左/右數據對齊

- 轉換數據輸出的有符號/無符號格式

- 中斷/DMA請求生成基於各種條件:

- -數據緩衝區等於或高於閾值

- -數據緩衝區溢出

- -WDG跨界事件

- 可編程閾值範圍WDG支持

- 低消耗模式

- 可選的轉換過程暫停機制在SoC調試請求

- 外部提供的時間戳添加到數據樣本

- 並行側接口與幾個片上配套模塊,如抽取濾波器或DSPL模塊通信

3.操作模式

以下介紹SDADC的不同操作模式。退出復位時,操作模式由模塊配置寄存器(MCR)決定。該模式通過將MCR[mode]位取反而進入。

3.1差分輸入模式

在這種模式下,一對模擬輸入分別連接到ADC調製器的正、負端。為了支持收益並且用於診斷的偏置校準,在這種模式下可以選擇兩個輸入端的固定偏置電壓。在系統重置退出後,如果認為MCR啟用了SDADC,則這是默認的操作模式。通過否定MCR[mode]進入該模式。差分輸入模式下,AIN[0:7]中的一對模擬輸入連接到SDADC調製器模塊的輸入端。模塊支持四種差分對:AIN[0,1],AIN[2,3],AIN[4,5]和AIN6,7]。調製器模塊有兩個輸入端子,正(INP)和負(INM)。輸入對的選擇取決於CSR的ANCHSEL欄位。它們之間的連通性給定差分對的模擬輸入,連接到正極還是負極,根據參考手冊表1013確定。差分輸入模式也可用於執行增益和偏置校準,其中輸入端子帶有來自偏置塊的固定電壓。

3.2單端輸入模式

該模式通過斷言MCR[mode]位進入。在該模式下,負輸入端根據MCR中的選擇信息偏置固定電壓,另一個模擬輸入端連接到所選的外部模擬通道。在該模式下,AIN[0:7]中的一個模擬輸入被CSR的ANCHSEL欄位選中並連接到正極。負輸入端偏置有固定的內部電壓。

3.3外部調製器模式

該模式通過斷言MCR[mode]位進入。在這種模式下,BSEXT/CLKEXT輸入引腳上可用的外部調製器的數據流和時鐘輸出直接路由到SDADC模塊。在這種模式下,內部調製器被繞過。僅使用SDADC的數字濾波器進行結果計算。外部調製器時鐘的源可以是內部片上時鐘源或來自外部調製器的直接時鐘輸出。這些引腳的外部引腳功能控制必須在器件的集成邏輯中配置,而不包括在SDADC數字接口中。當選擇外部調製器時,內部調製器可以通過取消MCR[EN]欄位來置於低消耗模式。在這種模式下,即使通過斷言MCR[TRIGEN]欄位啟用了硬體觸發輸入,也會忽略它。在MCR中編程的所有其他配置設置(如增益,抽取率,濾波器)對轉換沒有影響。

3.4 支持中斷請求

SDADC有一個條件生成中斷請求。當檢測到數據FIFO滿時,斷言DFFF欄位,表示存儲在數據FIFO中的轉換數據字數等於或大於FCR[FTHLD]值所指示的數據字數。只有當RSER[DFFDIRE]被斷言時,才會生成中斷請求。

數據FIFO溢出標誌(DFORF)表示FIFO溢出情況。當FIFO覆蓋功能時,無法接收進一步轉換的數據字並丟失數據是禁用的。只有當RSER[DFORIE]被斷言時,才會生成中斷請求。除此之外WDG閾值交叉事件還可以生成中斷請求。

如果設置了RSER[GGE],則只有當外部全局門控信號被斷言並且RSER[DIRFWGS]位為“0”時,所有模塊中斷請求才合格。

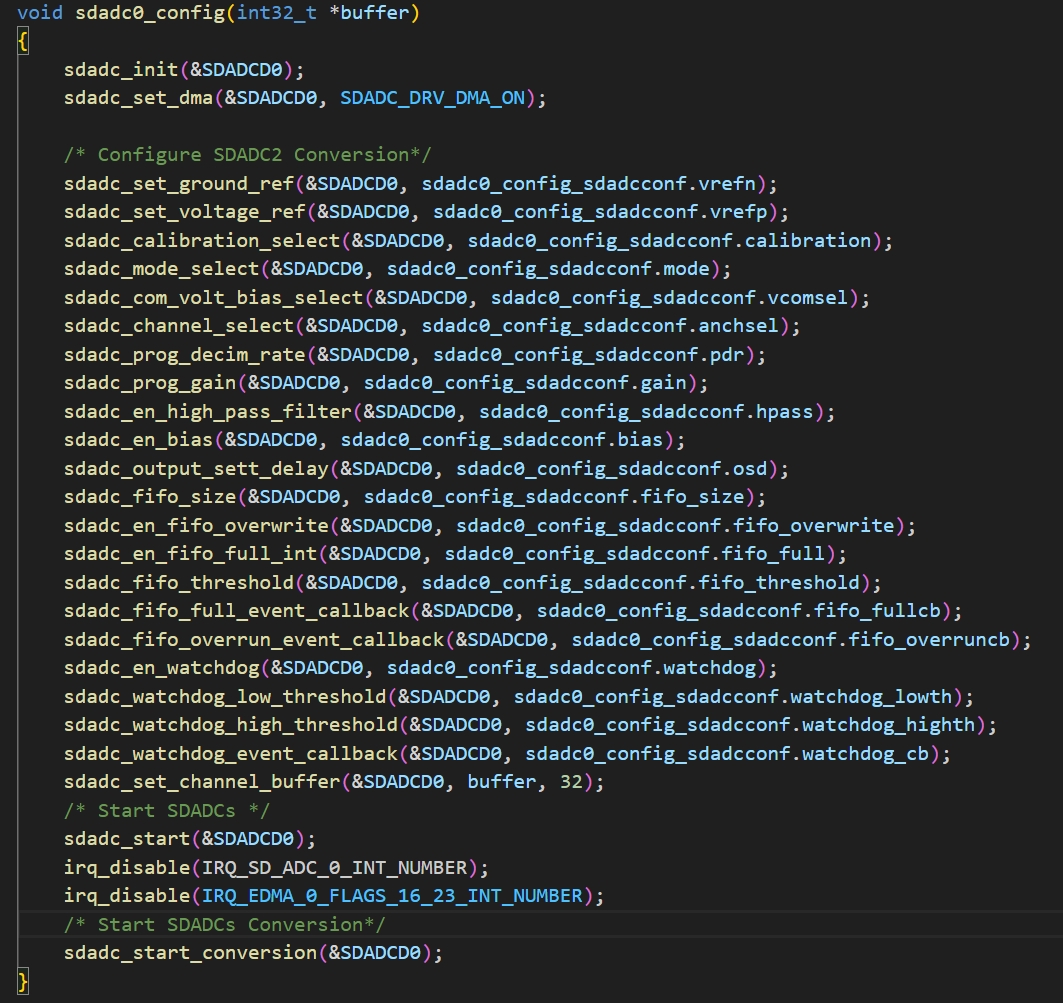

4.SDADC配置

配置參數如下:

|

SDADC configure |

parameter |

|

GND |

0.0 |

|

Voltage |

5.0 |

|

Calibration |

0(No self_test) |

|

Mode |

Differential mode |

|

ANCHSEL |

0(INP:AIN0,INM:AIN1) |

|

PDR |

0 |

|

Gain |

0(Gain=1) |

|

BIAS |

Enable |

|

OSD(output delay) |

32 |

|

High pass filter |

Enable |

|

FIFO |

Disable |

5.實驗結果

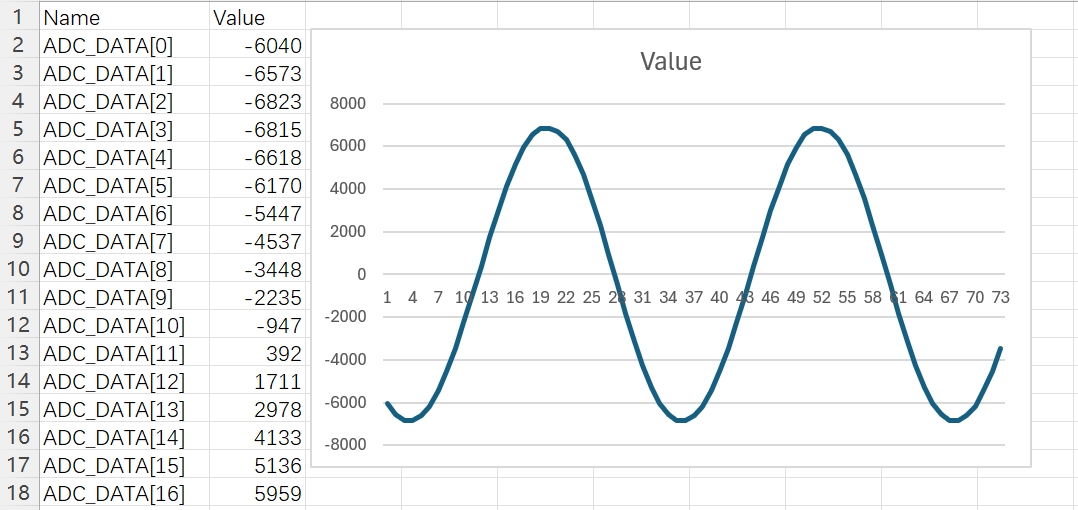

當SDADC接入一路差分正弦波信號時,數據順利採集如下:

評論