東京工業大學工學院和Socionext Inc. 展開合作,宣佈聯合開發設計世界上最小的全數位鎖相迴路(PLL)。 PLL是所有數位應用中的關鍵時鐘電路,不斷減小其尺寸並提高其性能是實現下一代技術發展的重要基礎。

人工智慧、5G蜂巢通信、物聯網等新興技術有望為社會帶來革命性變革。要做到這一點,高性能SoC必不可少。 SoC的核心組成部分是鎖相迴路(PLL),該電路通過與參考振盪器頻率同步並輸出相同或更高頻率的信號。 PLL統一整合時鐘信號,通過振盪充當節拍器,為數位設備的穩定運行提供精確的時序參考。

為實現高性能SoC,半導體工藝製程變得越來越複雜,如何借由縮小工藝節點來提高晶片性能是目前面臨的技術難點。半導體商競相投入開發更先進的製程來提高市場競爭力。目前,7 nm工藝製程晶片(比10 nm的前代產品有了重大改進)已經投入生產,5nm晶片的研發也早早地提上了日程。 然而,要實現更先進製程工藝晶片還存著一些技術瓶頸。現有的PLL需要類比元件,這些元件通常體積龐大並且難以實現小型化設計。

岡田健一教授領導的東京工業大學工學院和Socionext展開合作,通過分數N分頻PLL解決了這一技術難題。分數N分頻PLL僅需要數位邏輯門,而無需大量的類比組件,使得新的PLL非常適用在傳統積體電路中。

岡田教授及其團隊使用多種技術降低PLL所需面積、功耗和抖動(傳輸數位信號時影響性能的時間波動)。 為減小面積,他們採用了環形振盪器(易於縮小的緊湊型振盪器)。同時為減少抖動,使用了“注入鎖定”技術降低環形振盪器的相位雜訊(信號中的隨機波動),它能使振盪器在寬頻範圍內與外部信號同步時接近振盪器的頻率。此外,較低的相位雜訊還可降低功耗。

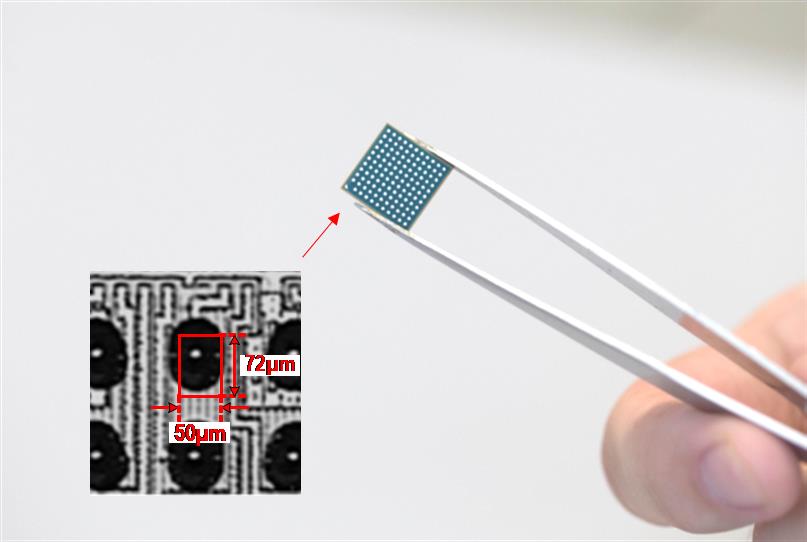

分數N分頻PLL的設計在許多方面都優於市面上的同類產品。 它以低功耗和小面積實現了最佳抖動性能(如下圖1所示)。 岡田教授表示:“該PLL的核心面積僅為0.0036 mm2,整個PLL只擁有一個電源。” 此外,它可以使用標準的數位設計工具進行構建,可實現快速、省力和低成本生產。

在商業落地方面,分數N分頻PLL可輕鬆集成至5nm以下先進制程工藝晶片中,其超高性能和低功耗的特點可以滿足人工智慧、物聯網等最前沿的新興技術應用。“我們的研究實驗證明了分數N分頻PLL的潛力。該設計方法還可以應用於設計各種SoC模組,如數據轉換器、電源管理電路、無線收發器等模組,大大提高設計生產率,並減少設計成本。” 岡田教授解釋說。東京工業大學和Socionext還將在此領域繼續展開合作,共同推進電子設備小型化,不斷進行技術革新。

這項研究工作同時與TeraPixel Technologies Inc.合作進行。

参考:

|

Bangan Liu1, Yuncheng Zhang1, Junjun Qiu1, Hongye Huang1, Zheng Sun1, Dingxin Xu1, Haosheng Zhang1, Yun Wang1, Jian Pang1, Zheng Li1, Xi Fu1, Atsushi Shirane1, Hitoshi Kurosu2, Yoshinori Nakane2, Shunichiro Masaki2, Kenichi Okada1 |

*Corresponding author’s email: okada@ee.e.titech.ac.jp

圖1:包含PLL的晶片圖

整個全數字PLL尺寸僅為50×72 µm2,是迄今為止最小的PLL