Chapter 1 CCM 的應用範圍Chapter 1 CCM 的應用範圍

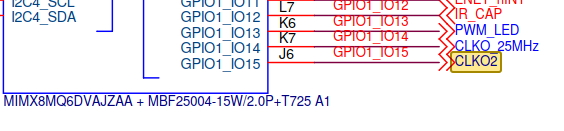

在 Reference Manual 的 Table 5-2. System Clocks and Gating 列出每一個 Module 會使用到的時鐘源,透過 CCM 應用來控制或調整 Module工作頻率,例如 GPIO 模組,本文章最後會實作一個簡單的 CCM 應用,將 GPIO_IO15 Pin 腳輸出特定頻率 37.125 MHz。

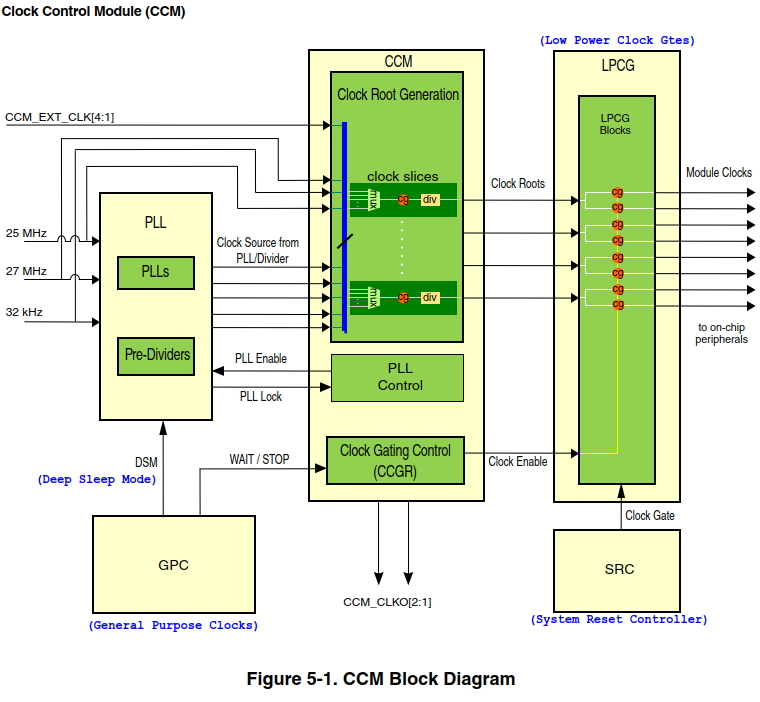

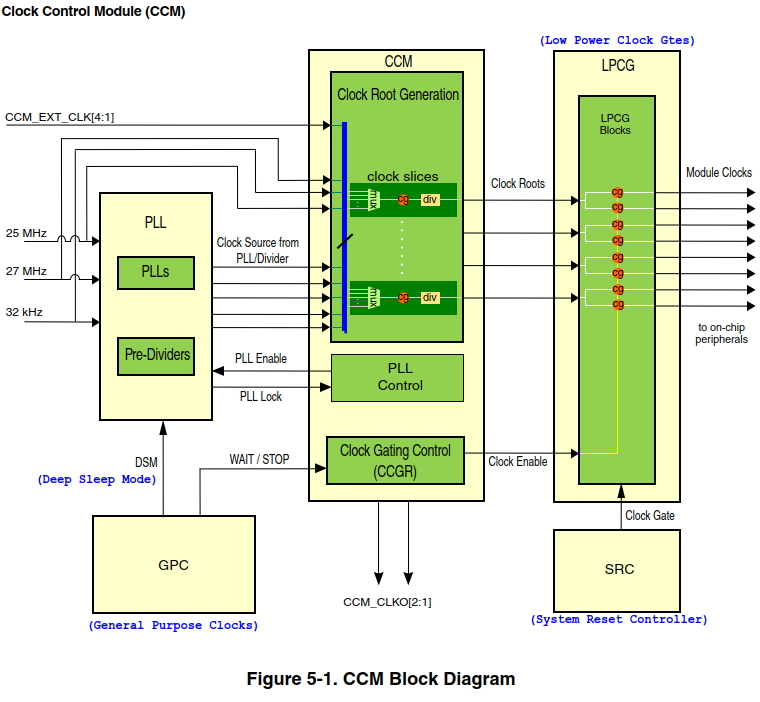

Chapter 2 CCM 的方塊圖

CCM 是管理一顆晶片的 Clock 模組,然後透過設定乘法器 & 除法器 & Gate 產生晶片內部匯流排和周邊模組所需的 Clock 。

Chapter 3 重要表格

3.1 Clock Root Selects

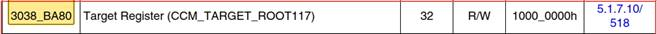

Table 5-1 列出每一個 Clock Root 可以選擇的 CLK來源和最大的頻率限制,一般會有 8 個訊號來源,Clock Slice 的編號就是 CCM Memory Map查表時,CCM_TARGET_ROOT 旁邊的編號,再借由 Section/Page 找到對應的控制暫存器,請參考下圖。

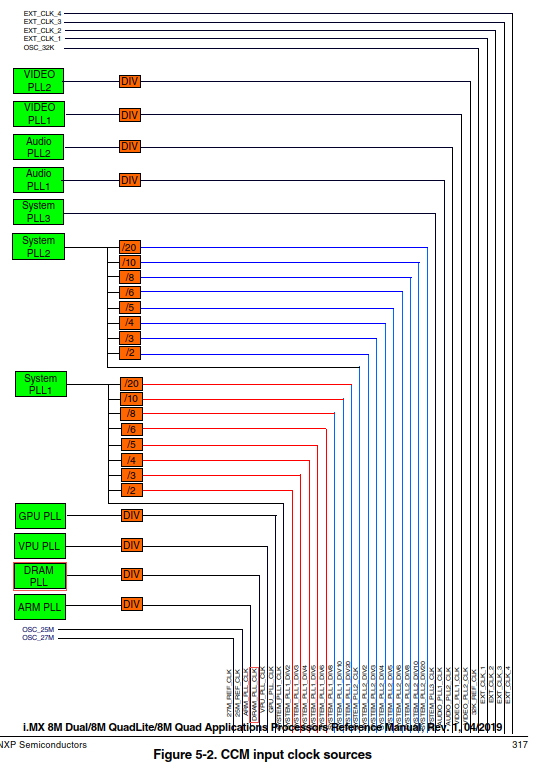

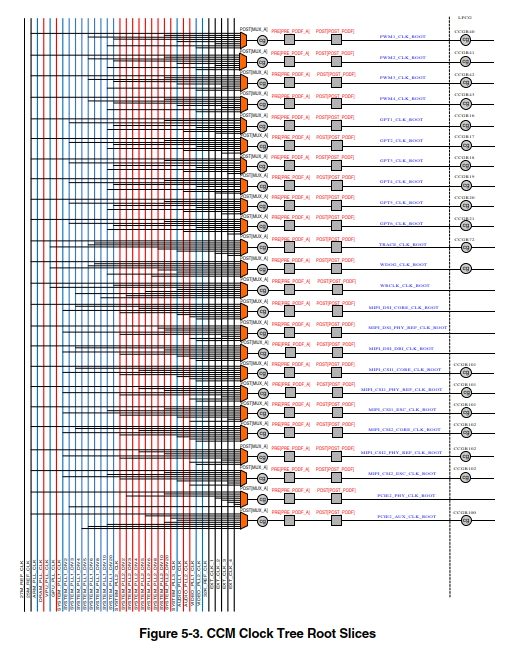

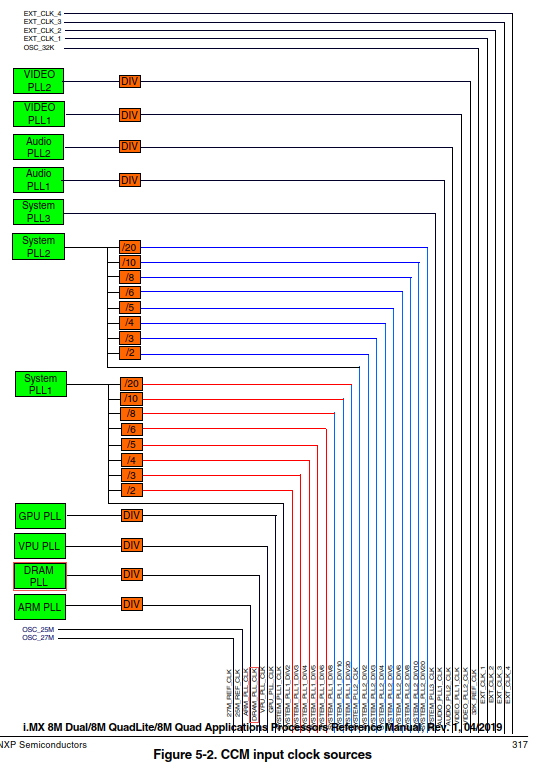

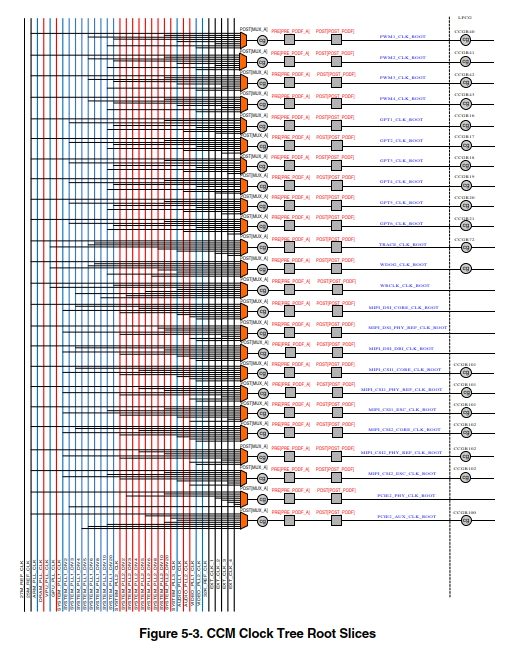

3.2 Clock Tree

Clock Root 的 Source Select 選擇器所組成 Clock Tree,可以由 Reference Manual 的 Figure 5-2 CCM Input Clock Source (圖一) 和 Figure 5-3. CCM Clock Tree Root Slices (圖二) 來直觀的了解架構和關係。

圖一

圖二

3.3 System Clocks

Reference Manual 的 Table 5-2. System Clocks and Gating 列出每一個 Module 會使用到 Clock Root 和 Gating (閘門) ,以下圖為例,可以知道常用的 I2C 模組中的 I2C1 Clock Root 是 ccm_i2c1_clk_root,並且由 CCGR23 Gating 控制開關。

配合 I2C 章節 Table 16-1. 的描述,Module Clock 的兩組 Clock Name 的意思和用途。

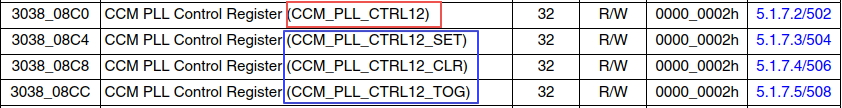

Chapter 4 Programming Guide

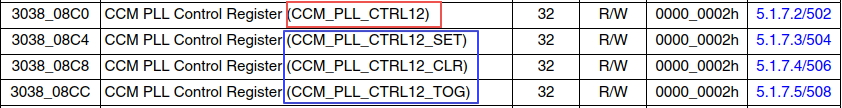

CCM 每一個 Register 是透過 Set、Clear、Toggle處理 Base Address 內部的值,因為 Base Address 內部的值是唯讀。

例如下圖要控制紅色框內 CCM_PLL_CTRL12 的值,必需透過藍色框內的 Register 來設定。

這些 Set、Clear、Toggle 的暫存器和 Base Addresss 的關係如下:

Base Addr : 3038 08C0

Set ---> Base Addr + 0x04

在 Reference Manual 的 Table 5-2. System Clocks and Gating 列出每一個 Module 會使用到的時鐘源,透過 CCM 應用來控制或調整 Module工作頻率,例如 GPIO 模組,本文章最後會實作一個簡單的 CCM 應用,將 GPIO_IO15 Pin 腳輸出特定頻率 37.125 MHz。

Chapter 2 CCM 的方塊圖

CCM 是管理一顆晶片的 Clock 模組,然後透過設定乘法器 & 除法器 & Gate 產生晶片內部匯流排和周邊模組所需的 Clock 。

Chapter 3 重要表格

3.1 Clock Root Selects

Table 5-1 列出每一個 Clock Root 可以選擇的 CLK來源和最大的頻率限制,一般會有 8 個訊號來源,Clock Slice 的編號就是 CCM Memory Map查表時,CCM_TARGET_ROOT 旁邊的編號,再借由 Section/Page 找到對應的控制暫存器,請參考下圖。

3.2 Clock Tree

Clock Root 的 Source Select 選擇器所組成 Clock Tree,可以由 Reference Manual 的 Figure 5-2 CCM Input Clock Source (圖一) 和 Figure 5-3. CCM Clock Tree Root Slices (圖二) 來直觀的了解架構和關係。

圖一

圖二

3.3 System Clocks

Reference Manual 的 Table 5-2. System Clocks and Gating 列出每一個 Module 會使用到 Clock Root 和 Gating (閘門) ,以下圖為例,可以知道常用的 I2C 模組中的 I2C1 Clock Root 是 ccm_i2c1_clk_root,並且由 CCGR23 Gating 控制開關。

配合 I2C 章節 Table 16-1. 的描述,Module Clock 的兩組 Clock Name 的意思和用途。

Chapter 4 Programming Guide

CCM 每一個 Register 是透過 Set、Clear、Toggle處理 Base Address 內部的值,因為 Base Address 內部的值是唯讀。

例如下圖要控制紅色框內 CCM_PLL_CTRL12 的值,必需透過藍色框內的 Register 來設定。

這些 Set、Clear、Toggle 的暫存器和 Base Addresss 的關係如下:

Base Addr : 3038 08C0

Set ---> Base Addr + 0x04

Clear ---> Base Addr + 0x08

Toggle ---> Base Addr + 0x0c

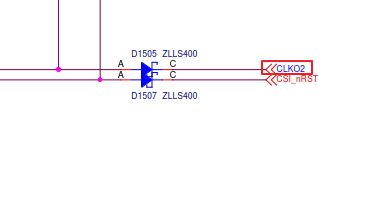

Chapter 5 實作 (i.MX8MQ EVK 驗證)

1. 由 CLKO2 Pin 腳輸出 Clock 頻率 37.125 MHz

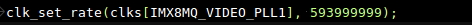

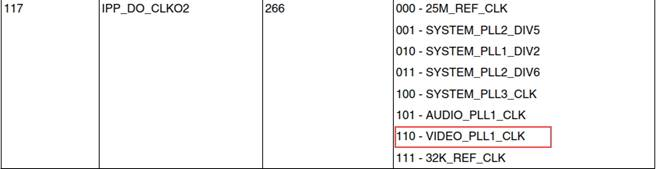

2. 在 clk-imx8mq.c 檔案裡,IMX8MQ_VIDEO_PLL1 可以被 37.125 M 整除,所以決定作為 Clock 來源。

594000000 / 16 = 37125000 = 37.125 MHz

tmp/work/imx8mqevk-poky-linux/linux-imx/4.14.98-r0/git/drivers/clk/imx/clk-imx8mq.c

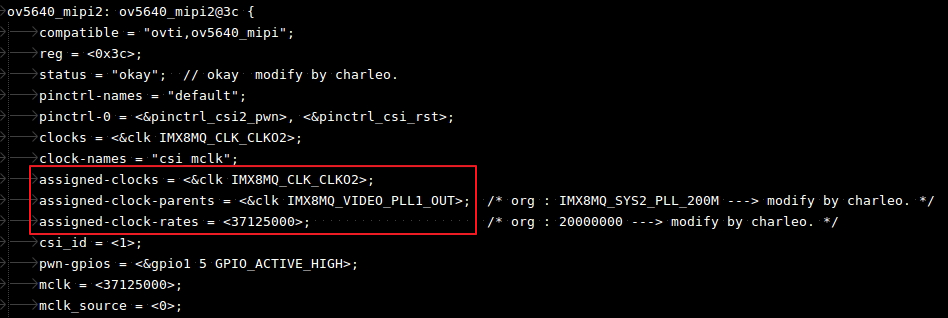

3. Device Tree 如下修改:

tmp/work/imx8mqevk-poky-linux/linux-imx/4.14.98-r0/git/arch/arm64/boot/dts/freescale/fsl-imx8mq-evk.dts

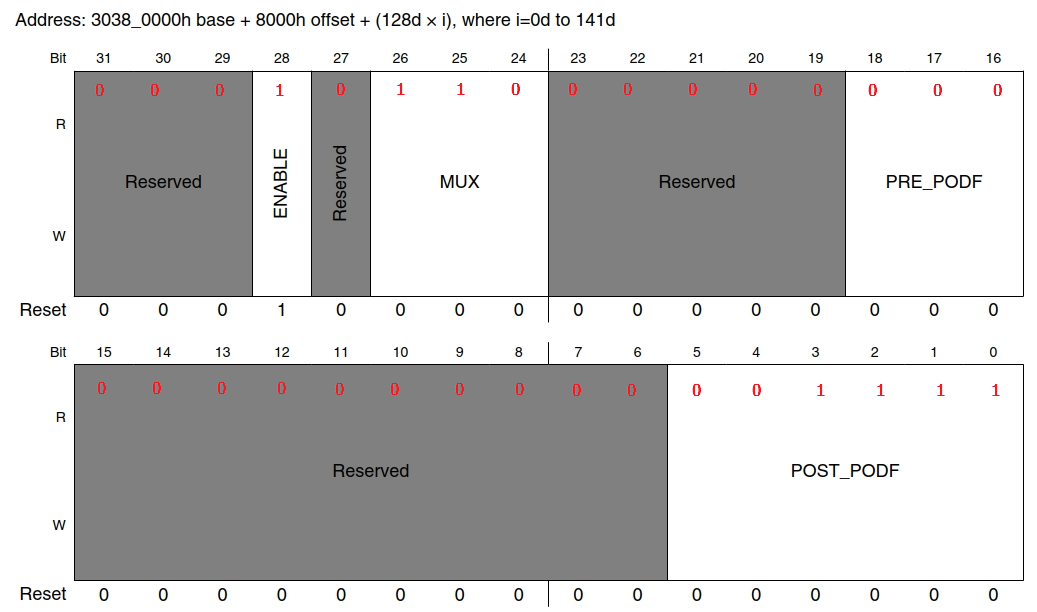

4. 確認 Register 狀態:

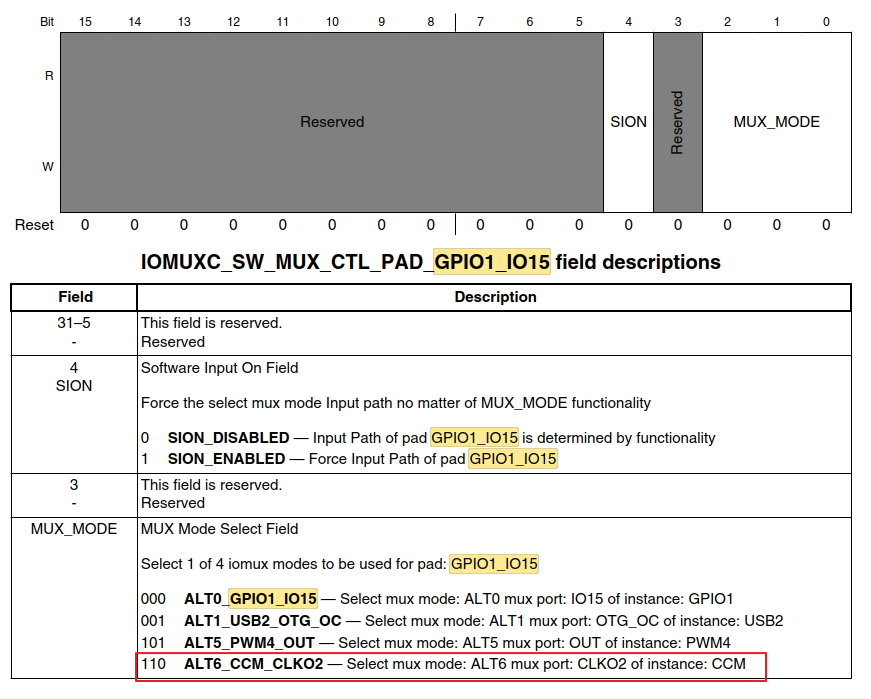

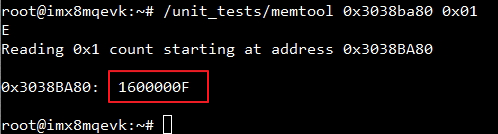

(1) GPIO_IO15 Pin 腳功能切換到 CLKO2 模式

(2) CCM Register 狀態符合輸出設定

5. 輸出波型如下:

Chapter 6 參考資料

1. IMX8MDQLQRM.pdf (Rev1.0)

參考來源