推進摩爾定律設限 3D封裝技術已成關鍵

隨著先進奈米製程已逼近物理極限,摩爾定律發展已難以為繼,無法再靠縮小線寬同時滿足性能、功耗、面積及訊號傳輸速度等要求;再加上封裝技術難以跟上先進製程的發展進程,因此三星、台積電、英特爾等晶圓代工巨擘紛紛跨足封裝領域,要借重先進的封裝技術實現更高性能、更低耗電量、更為小體積、訊號傳輸速度更快的產品。

甚至,在逐步進入後摩爾定律時代後,晶圓代工大廠的發展重心,也逐漸從過去追求更先進奈米製程,轉向封裝技術的創新。由於高度性能計算(high-performance computing, HPC)晶片的需求正在急遽增加,因此,數據中心和雲端計算基礎架構變得至關重要,尤其是可支持新的高性能技術的AI和5G設備。但這些設備面臨的挑戰是,該設備及其多核心架構的高效能,將會附帶有高寬頻密度和低延遲的問題。而異質整合成為HPC晶片需求飆升的因素,並為3D IC封裝技術打開嶄新的一頁。

何謂3D封裝 跟2.5D封裝差異又在哪裡

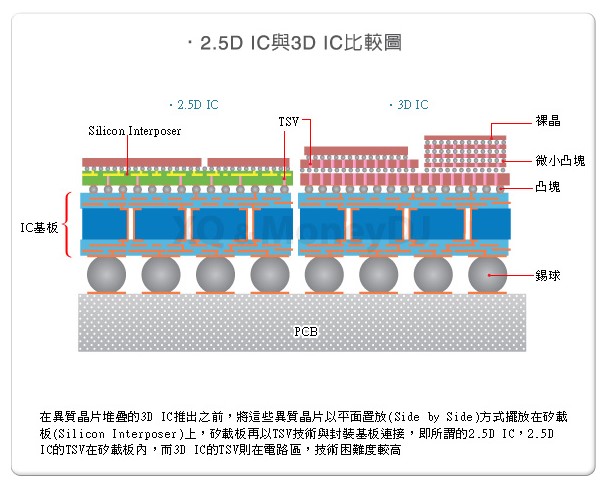

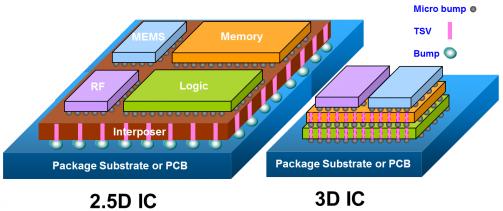

矽通孔技術(TSV)實現Die與Die間的垂直互連,通過在Si上打通孔進行晶片間的互連,無需引線鍵合,有效縮短互連線長度,減少信號傳輸延遲和損失,提高信號速度和帶寬,降低功耗和封裝體積,是實現多功能、高性能、高可靠性且更輕、更薄、更小的晶片系統級封裝。

由於3D TSV封裝工藝在設計、量產、測試及供應鏈等方面還不成熟,且工藝成本較高,目前業界採用介於2D和3D之前的2.5D連接層封裝形式,通過在Die和基板間添加一層連接層,大幅度提高封裝的輸入輸出(I/O)信號密度,是3D TSV封裝大規模商用之前既經濟又實用的方案。

延伸閱讀 Monkey的其他博文

先進封裝製程WLCSP-Warpage Wafer 該如何克服?

先進封裝製程WLCSP-BGBM製程

先進封裝製程WLCSP-TAIKO製程

先進封裝製程WLCSP-FSM製程

3D封裝技術 各家實力較勁意味濃厚

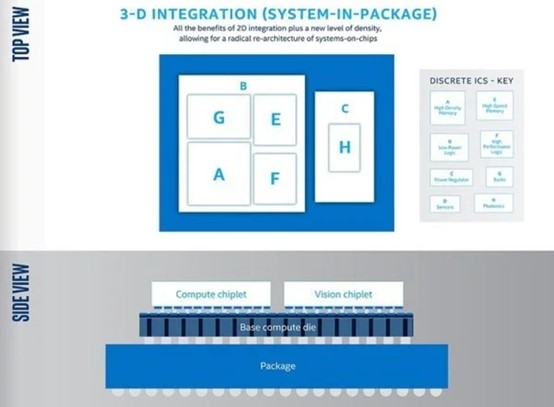

英特爾副總裁Koushik Banerjee指出,利用異質整合技術於單系統級封裝(SiP),將可以透過多個處理技術節點,實現業界長期以來對矽智財(silicon intellectual property)、晶片功能、以及低耗能和高頻低延遲的晶片需求。

英特爾計畫推出首款Foveros 3D封裝產品,該產品是將10奈米的HPC晶片與低耗能的22奈米基本晶片互相結合,並在頂部堆疊記憶體,形成一種嵌入式多晶片互連橋(Embedded Multi-Die Interconnect Bridge, EMIB)的組合。

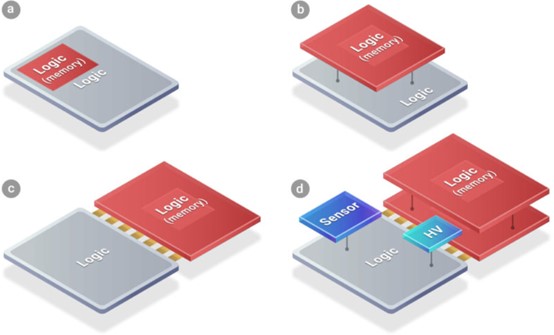

台積電則繼續升級其基板上晶片(Chip-on-Wafer-on-Substrate, CoWoS)、扇出型晶圓(Integrated Fan-out, InFO)、和其他2.5D的IC生產解決方案,同時開發SoIC和WoW(wafer-on-wafer)等3D晶片堆疊技術。

其實,台積電的SoIC基於Chip-on-Wafer概念,具有支持一對多或不同製程節點的靈活性,而其WoW集成了兩個晶圓,產量時更穩定,可用於相同尺寸的產品,或由成熟的製程技術進行製造。

早期(2013 年以前)2.5D TSV封裝技術主要應用於邏輯模塊間集成,FPGA晶片等產品的封裝,集成度較低。到2014年業界的3D TSV封裝技術己有部分應用於內存的晶片封裝,用於大容量內存晶片堆疊,同時應用於高性能晶片的高端消費產品中。2015年,2.5D TSV技術開始應用於一些高端的圖形處理器(GPU)/中央處理器(CPU)以及網絡晶片中,同時"應用處理器(AP)+ 內存"的集成晶片也開始有部分採用2.5D TSV封裝,業界在連接層的成本控制和加工能力方面有一定提高。

高端手機晶片、大規模I/O的晶片以及高性能晶片中將實現3D TSV封裝,同時目前3D封裝成本較高的因素也會解決,有望逐步實現大規模量產。

台積電TSMC 3D封測廠2021年運轉

台積電竹南封測廠第一期廠區預計2021年5月完工,總投資額估計超過新台幣3032億元,估計將可創造1000個以上就業機會。由於,看好AI及HPC 發展趨勢,3D封裝技術成為開發目標。

所謂 3D 封裝技術,主要為求再次提升 AI 之 HPC 晶片的運算速度及能力,試圖將 HBM 高頻寬記憶體與 CPU / GPU / FPGA / NPU 處理器彼此整合,並藉由高端 TSV(矽穿孔)技術,同時將兩者垂直疊合在一起,減小彼此的傳輸路徑、加速處理與運算速度,提高整體 HPC 晶片的工作效率。除了封測廠(日月光、力成、Amkor等)積極加入外,半導體代工製造商(台積電、三星、美光等)與 IDM 廠(Intel)也陸續投入3D封裝技術研發及資源。

參考來源