一、簡介

NXP KW45 是一款高性能、低功耗的無線 MCU,其低功耗設計非常適合電池供電的應用,可以延長設備的電池壽命。此外它還具有出色的射頻性能,支持多種天線設計和射頻匹配,以實現穩定的無線連接和優秀的抗干擾性能。為了能夠儘可能的發揮其全部性能,作為晶片應用者來說,一個好的硬體設計是必不可少的。那麼本篇博文將從 KW45 的硬體設計上一些著重需要注意的方面做一個小小的概述,希望能夠給即將應用到這顆晶片的設計師提供一些參考。

二、封裝

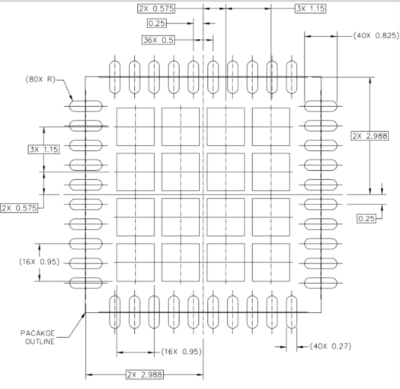

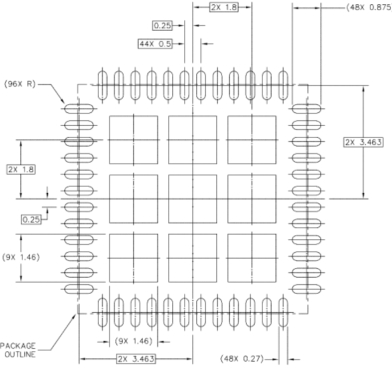

KW45 從引腳數分為兩種封裝,一種是 40PIN(6*6,間距 0.5mm) 的 HVQFN,一種是 48PIN(7*7,間距 0.5mm) 的 HVQFN。40PIN 封裝的有 16 個中心接地焊盤,48PIN 封裝的有 9 個中心接地焊盤,需要按照封裝圖設計 0.25mm 的通孔將其連接到地層,這對於射頻接地是必需的。

圖 1 HVQFN 40PIN(引自 NXP 官方資料)

圖 2 HVQFN 48PIN(引自 NXP 官方資料)

三、腳位

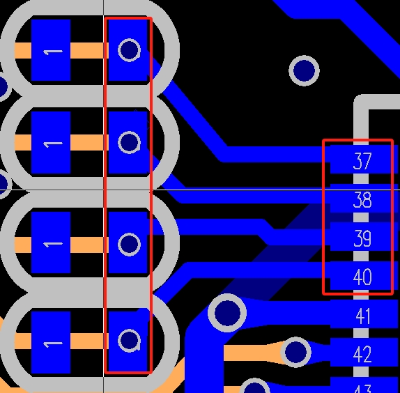

1. 如果在應用中使用到了 PTC1、2、3、4 這四個引腳,則必須在這四個引腳上分別加一個 3pF 的去耦電容,並且儘可能的靠近 KW45 晶片放置,這種設計是為了提高晶片的 EMC 性能。

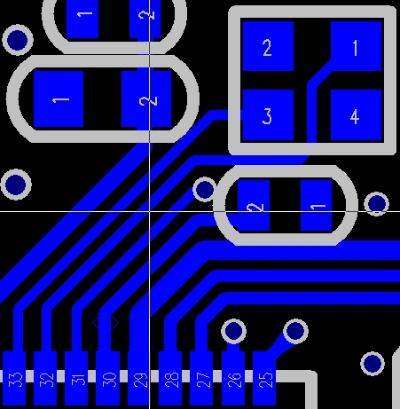

2. 晶振引腳,對於 32M 晶振來說,應當儘可能的靠近 KW45 放置,並且 XTAL&XTAL_OUT 設計儘量等長度類似差分線的設計,以此保證晶振信號的穩定性。

3. VDD_DCDC 引腳上設計的去耦電容放置儘可能靠近 MCU 引腳,VDD_RF 上放置的電容容值為 12pF。

4. 射頻信號線

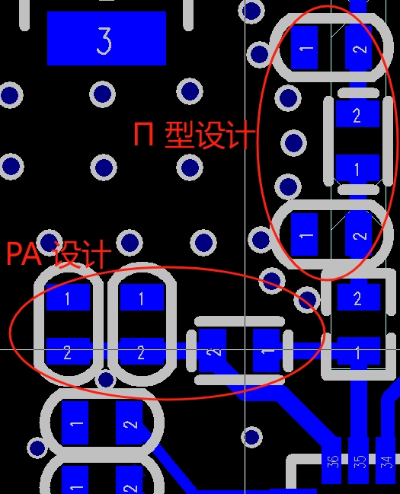

• 建議預留兩個 π 型設計,分別用於 MCU 端的射頻阻抗匹配和天線端的射頻阻抗匹配。

• 射頻信號信號線在制板時應當提出要求 50Ω 的阻抗設計。

• 建議使用參數為,介電常數 4.3,頂層(射頻線層)厚度大於 8~10mil 的 FR4 板材。

• 射頻信號線使用地過孔進行隔離。

• PA 設計嚴格准尋示例布局擺放(參考 NXP-KW45-EVK)。

圖 5 射頻設計

5. 堆疊結構

如果設計為兩層 PCB 板,那麼建議的堆疊結構為:

- 頂層:傳輸線、信號和接地的射頻線

- 底層:射頻參考線、信號線、地線

如果設計為四層 PCB 板,那麼建議的堆疊結構為:

- 頂層:射頻信號線

- L2:射頻參考地

- L3:電源線

- 底層:信號線

四、天線

1. 對於無線系統來說天線設計具有多樣性,包括板載天線和外置天線,各有優缺點,需要根據應用場景來選取更加合適的天

線類型。

2. 天線的最小回波損耗必須以 2440MHz 為中心頻點,並且回波損耗值為 -10dB 以下為佳。

3. 天線阻抗設計為 50 Ω。

4. 天線周邊應當遠離金屬器件,防止對射頻信號的干擾。

五、總結

以上就是博主在應用設計 KW45 時,根據恩智浦晶片原廠給出的設計規範做出的一些關鍵性總結,不免有些遺漏之處,以及設計經驗上的不足之處,更加詳細準確的設計事項還是需要多多的閱讀恩智浦官方給出的文檔。

參考資料:

1. KW45 Data Sheet.pdf

2. KW45B41Z-EVK_SCH.pdf

3. AN13227 Hardware Design Considerations.pdf

評論